SPI(Serial Peripheral Interface)即串行外设接口, 是一种单片机外设芯片串行扩展接口,也是一种高速、全双工、同步通信总线,所以可以在同一时间发送和接收数据。广泛用于嵌入式系统中连接微控制器和外部设备,实现数据的传输和通信。

1.SPI信号线(四根)

2.SPI常见分类

①SPI

通常我们说的SPI就是Standard SPI,有4根信号线,分别为CLK、CS、MOSI和MISO,也就是上面介绍的SPI协议。

②Dual SPI

Dual SPI是SPI Flash的一种特殊模式,旨在提高数据传输速率。在标准的SPI通信中,MOSI和MISO是独立的全双工线路,但在SPI Flash的应用中,由于Flash芯片通常是半双工工作的(即在同一时刻只能发送或接收数据,但不能同时进行),因此Dual SPI模式利用了这一特性,将MOSI和MISO重新定义为SIO0和SIO1,使得在单个时钟周期内可以并行地发送和接收数据。

在Dual SPI模式下,Flash芯片通常需要先接收一个特定的命令字节来进入这种模式。一旦进入Dual SPI模式,每个时钟周期就可以传输2个bit的数据(一个bit通过SIO0发送,另一个bit通过SIO1接收),从而实现了数据传输速率的加倍。

③ Queued SPI (QSPI)

Queued SPI,或简称QSPI,是Dual SPI的进一步扩展。在QSPI中,除了SIO0和SIO1之外,还增加了SIO2和SIO3两根I/O线,使得在单个时钟周期内可以传输4个bit的数据。这种设计进一步提高了数据传输的速率,特别适用于需要高速数据访问的Flash存储应用。

QSPI不仅提高了数据传输速率,还通过引入命令队列等特性,优化了Flash的访问效率。在QSPI中,主设备可以一次性向Flash发送多个命令和数据块,Flash芯片则按照命令队列的顺序依次执行,从而减少了主设备和Flash之间的交互次数,提高了整体的系统性能。

总结:

Dual SPI和QSPI是针对SPI Flash接口的特殊优化模式,它们通过改变数据线的使用方式和增加数据线的数量,将原本的全双工通信模式改为更适合Flash特性的半双工并行通信模式,从而实现了数据传输速率的显著提升。这些优化模式特别适用于需要高速数据访问的嵌入式系统和存储设备中。

(1)标准SPI是通用的,Dual SPI和QSPI只适用于flash;

(2)标准SPI:标准4线连接,全双工,同时收和发;

(3)Dual SPI:标准4线连接,半双工,2根数据线,并线发和收,双方向切换;

(4)QSPI:标准4线连接,半双工,4根数据线,并线发和收,双方向切换;

3.SPI通信协议

1.通信原理

SPI通信协议利用时钟信号的同步作用,实现数据在多个设备之间的传递。主设备通过时钟线(SCK)来规定数据的传输时序,并利用数据线(MOSI、MISO)进行数据的传输。同时,通过片选信号线(CS/SS)来选择与哪个从设备进行通信。

SPI通信的传输方式主要有两种:主设备驱动(Master)和从设备驱动(Slave)。

1. 主设备驱动(Master-driven):在主设备驱动模式下,主设备控制整个通信过程。它通过SCLK线提供时钟信号,同时向MOSI线发送数据,从MISO线接收数据。主设备还通过控制SS线选择要通信的从设备。

2. 从设备驱动(Slave-driven):在从设备驱动模式下,每个从设备在主设备的控制下依次发送和接收数据。主设备通过选择相应的SS线来选择与当前通信的从设备,然后发送数据到MOSI线,并从MISO线接收从设备的响应。

2.通信过程

- 启动通信:主设备通过拉低CS/SS(片选信号)线来选中特定的从设备,启动与该从设备的通信。此时,其他未被选中的从设备将忽略SPI总线上的通信。

- 时钟信号同步:主设备生成SCK(时钟信号)并控制其频率和极性(CPOL),以及相位(CPHA),从而定义数据的采集时机(上升沿或下降沿)。从设备根据SCK的时钟信号同步地发送和接收数据。

- 数据发送与接收:主设备将要发送的数据写入其SPI发送缓冲区,并通过MOSI(主设备输出/从设备输入)信号线将数据一位一位地移出。同时,通过MISO(主设备输入/从设备输出)信号线接收从设备发送的数据。从设备也通过其SPI发送缓冲区将数据通过MISO信号线发送给主设备,并通过MOSI信号线接收主设备发送的数据。数据的发送和接收是同步进行的,即每个SCK时钟周期内,主设备和从设备都各自发送和接收一位数据。

- 数据交换完成:当一个字节(或指定的数据长度)的数据交换完成后,主设备可以发送下一个字节的数据,或者通过拉高CS/SS线来结束与当前从设备的通信。

3.时钟信号的相位和极性

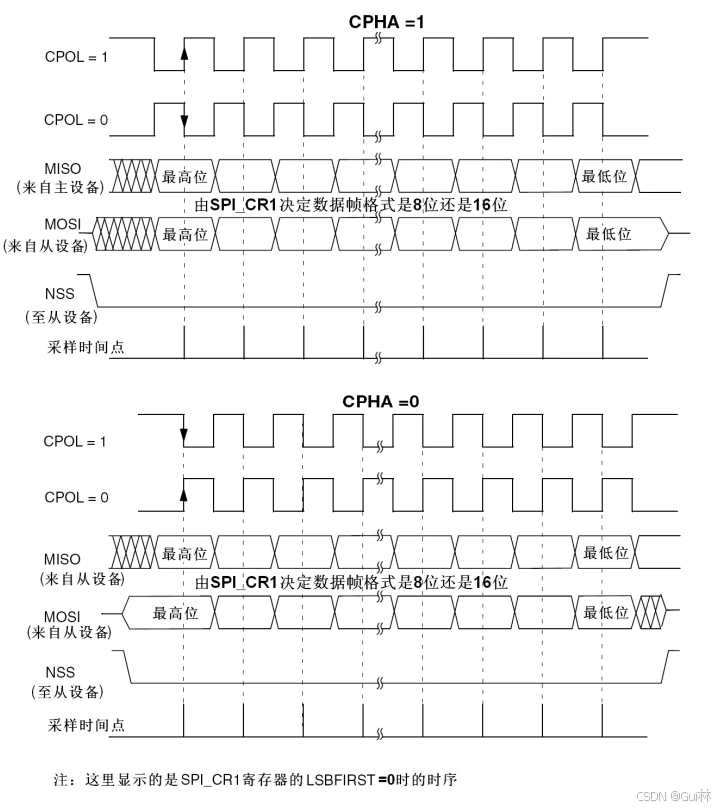

SPI_CR寄存器的CPOL和CPHA位,能够组合成四种可能的时序关系。 CPOL(时钟极性)位控制在没有数据传输时时钟的空闲状态电平,此位对主模式和从模式下的设备都有效。如果CPOL被清’0’, SCK引脚在空闲状态保持低电平;如果CPOL被置’1’, SCK引脚在空闲状态保持高电平。如果CPHA(时钟相位)位被置’1’, SCK时钟的第二个边沿(CPOL位为0时就是下降沿, CPOL位为’1’时就是上升沿)进行数据位的采样,数据在第二个时钟边沿被锁存。如果CPHA位被清’0’, SCK时钟的第一边沿(CPOL位为’0’时就是上升沿, CPOL位为’1’时就是下降沿)进行数据位采样,数据在第一个时钟边沿被锁存。

CPOL时钟极性和CPHA时钟相位的组合选择数据捕捉的时钟边沿。

下图显示了SPI传输的4种CPHA和CPOL位组合。此图可以解释为主设备和从设备的SCK脚、MISO脚、 MOSI脚直接连接的主或从时序图。

注意:

1. 在改变CPOL/CPHA位之前,必须清除SPE位将SPI禁止。

2. 主和从必须配置成相同的时序模式。

3. SCK的空闲状态必须和SPI_CR1寄存器指定的极性一致(CPOL为’1’时,空闲时应上拉SCK为高电平; CPOL为’0’时,空闲时应下拉SCK为低电平)。

4. 数据帧格式(8位或16位)由SPI_CR1寄存器的DFF位选择,并且决定发送/接收的数据长度。

5. STM32H750 的 SPI 功能很强大, SPI 时钟最高可以到 45MHz,支持 DMA,可以配置为 SPI 协议或者 I2S 协议(支持全双工 I2S)

数据时钟时序图

4.关于SPI中的读和写:

SPI通信中确实没有单独的读或写操作命令,而是通过数据的发送和接收来同步完成数据的读写。

如果主设备只想向从设备写入数据而不关心从设备的响应,它可以忽略MISO线上接收到的数据(通常作为虚拟数据或无效数据处理)。

如果主设备想从从设备读取数据,它必须发送一个“虚拟”的字节(通常是一个预定义的命令或地址)来触发从设备发送数据。这个“虚拟”字节的发送对于从设备来说可能是一个写操作的结束信号或读操作的开始信号,具体取决于从设备的实现。

重要的是,无论主设备是否关心从设备的响应,它都必须发送数据以维持SPI通信的同步性。同样,从设备也必须响应主设备的时钟信号并发送数据,即使这些数据对主设备来说是无关紧要的。

FLASH 是存储芯片的一种,通过特定的程序可以修改里面的数据。FLASH 存储器又称闪存,它结合了 ROM 和 RAM 的长处,不仅具备电子可擦除可编程(EEPROM)的性能,还可以快速读取数据(NVRAM 的优势),使数据不会因为断电而失去。

W25Q128 将 16M 的容量分为 256 个块(Block),每个块大小为 64K 字节,每个块又分为 16 个扇区(Sector),每个扇区 4K 个字节。W25Q128 的最少擦除单位为一个扇区,也就是每次必须擦除 4K 个字节。操作需要给 W25Q128 开辟一个至少 4K 的缓冲区,对 SRAM要求比较高,要求芯片必须有 4K 以上 SRAM 才能很好的操作。

W25Q128 的擦除周期多达 10W 次,具有 20 年的数据保存期限,支持电压为 2.7V~ 3.6V,支持标准的 SPI,还支持双输出/四输出的 SPI,最大 SPI 时钟可以到 80MHz(双输出时相当于 160MHz,四输出时相当于 320M)。

1.W25QXX.c文件

2.W25QXX.h头文件

使用STM32H7将外部flash(W25Q64),使用hal库来配置SPI的初始化。

1.FlashDev.c

2.FlashPrg.c

PS:下载算法....

到此这篇console线引脚定义(console口引脚定义)的文章就介绍到这了,更多相关内容请继续浏览下面的相关推荐文章,希望大家都能在编程的领域有一番成就!版权声明:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若内容造成侵权、违法违规、事实不符,请将相关资料发送至xkadmin@xkablog.com进行投诉反馈,一经查实,立即处理!

转载请注明出处,原文链接:https://www.xkablog.com/cjjbc/12668.html