导出3D版的PDF!!!!

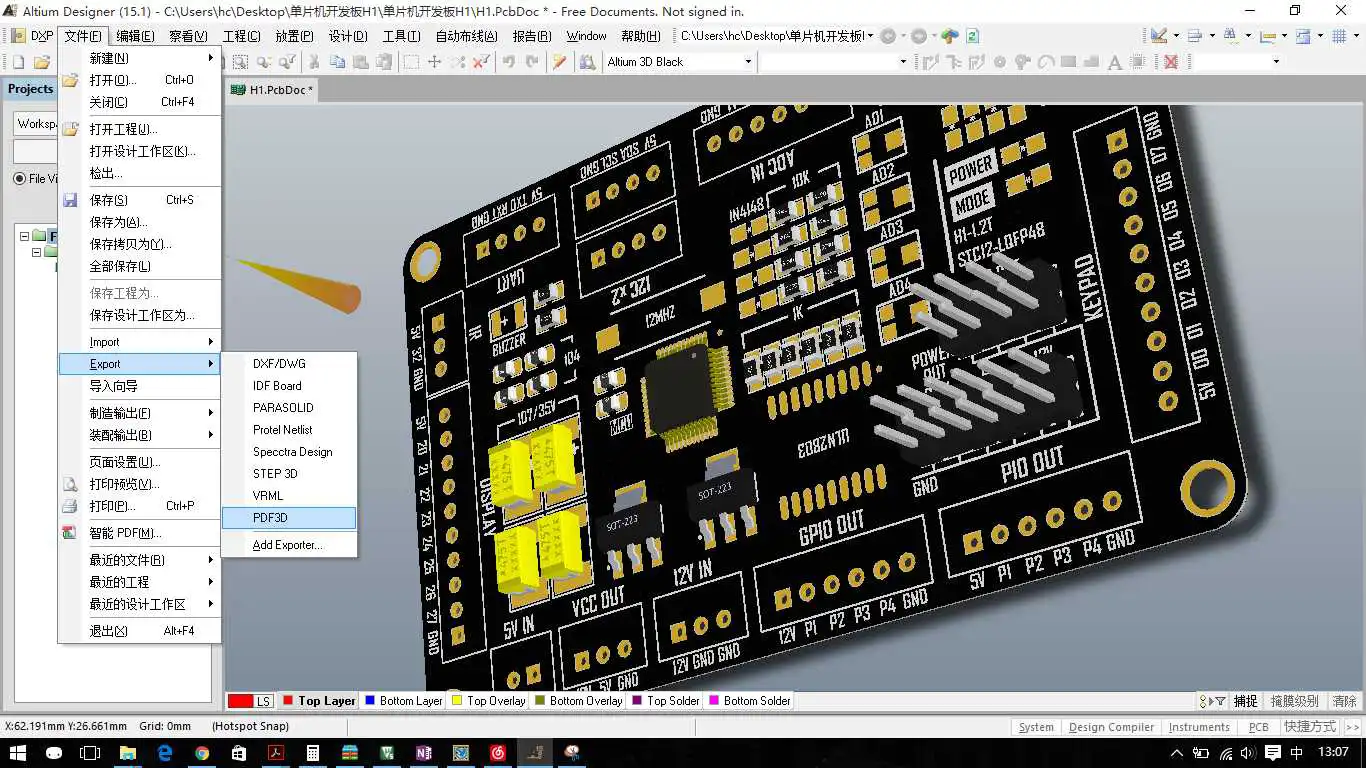

导出3D版的PDF!!!!

导出3D版的PDF!!!!

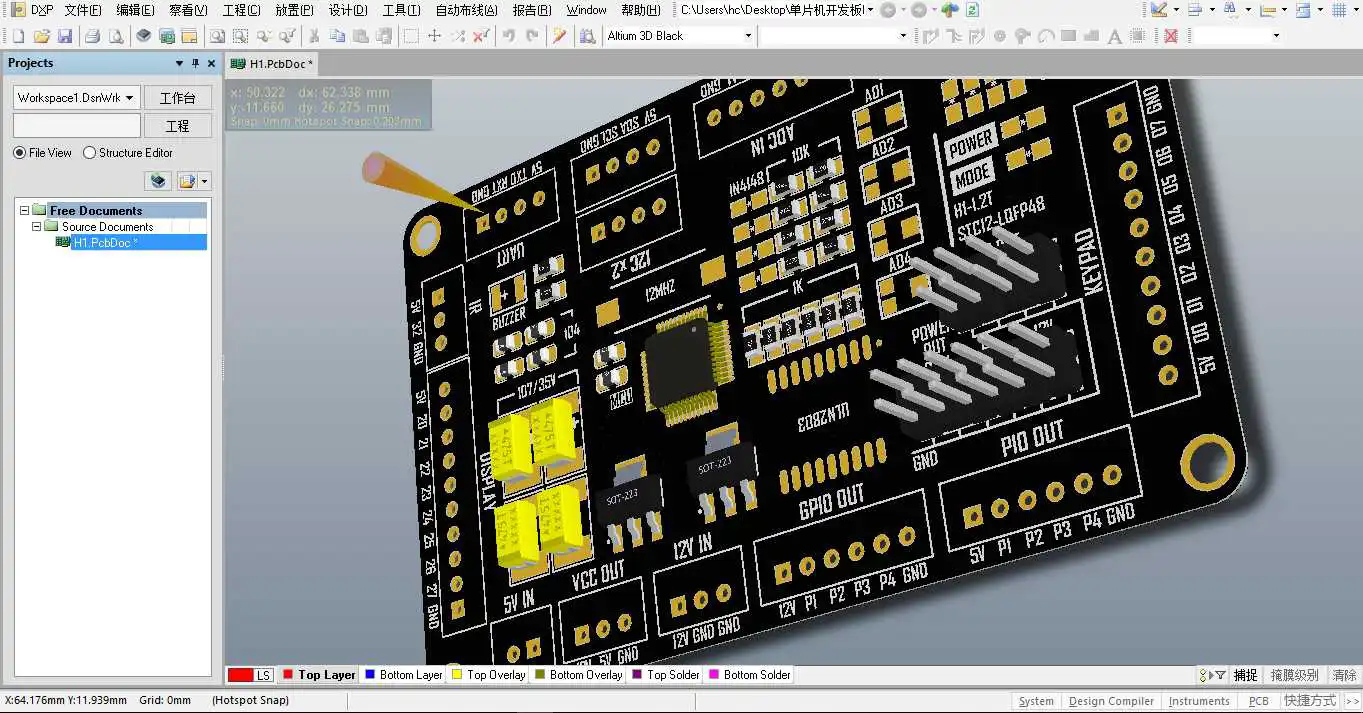

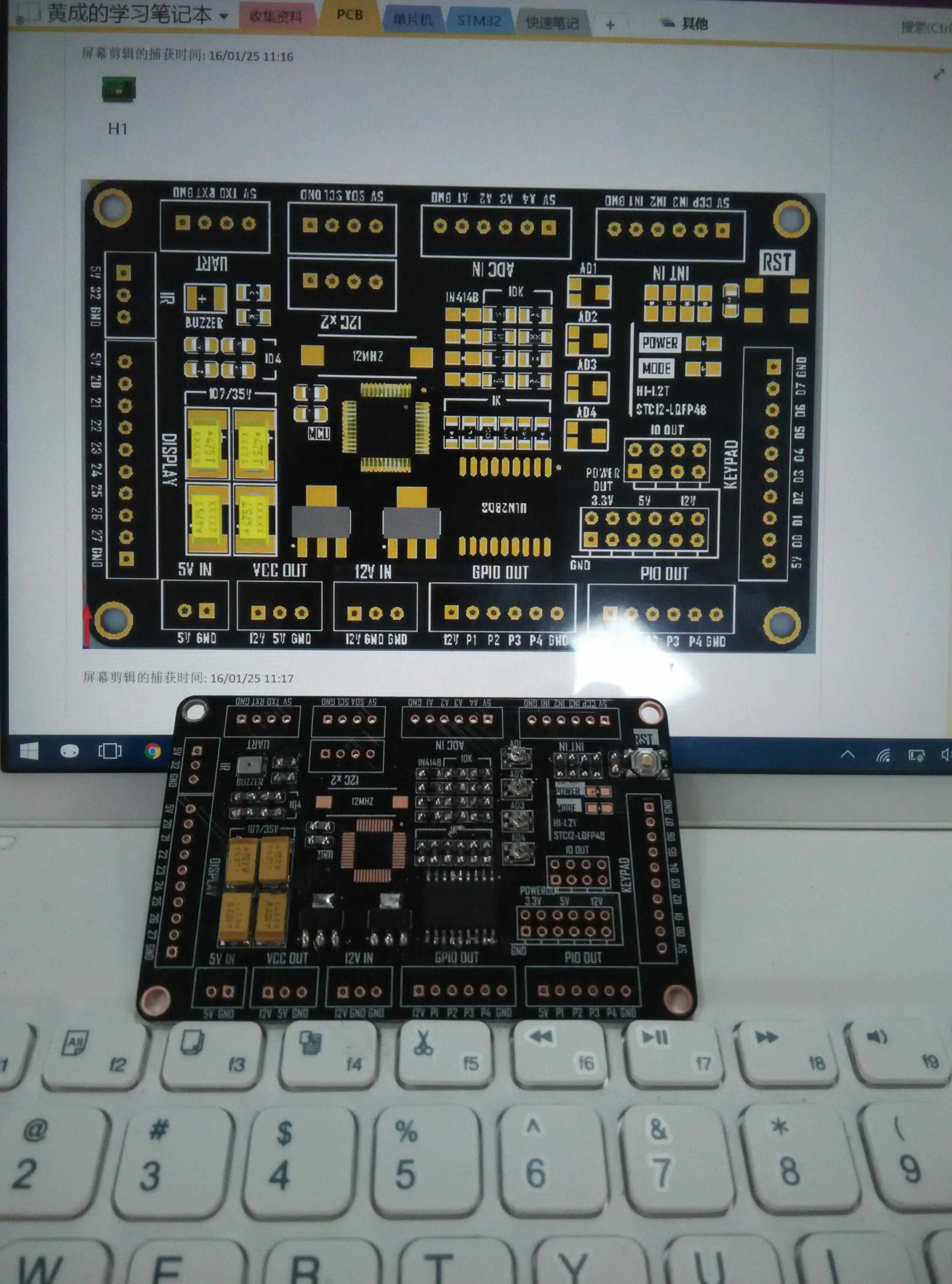

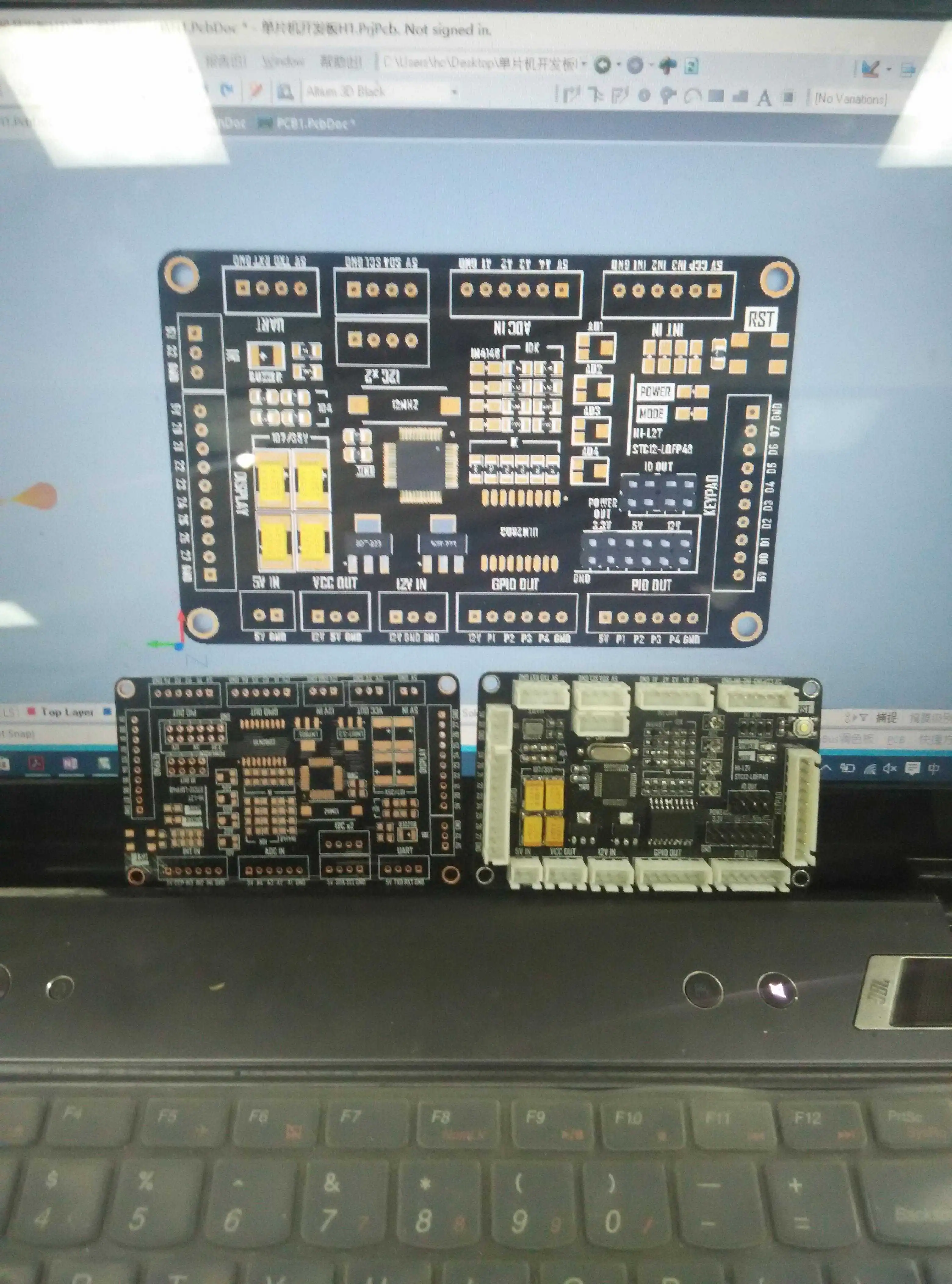

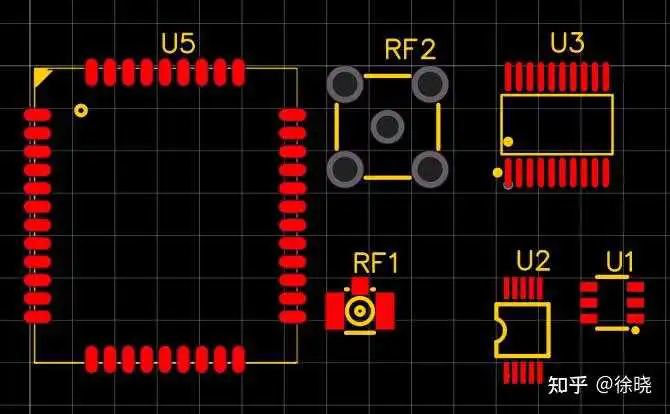

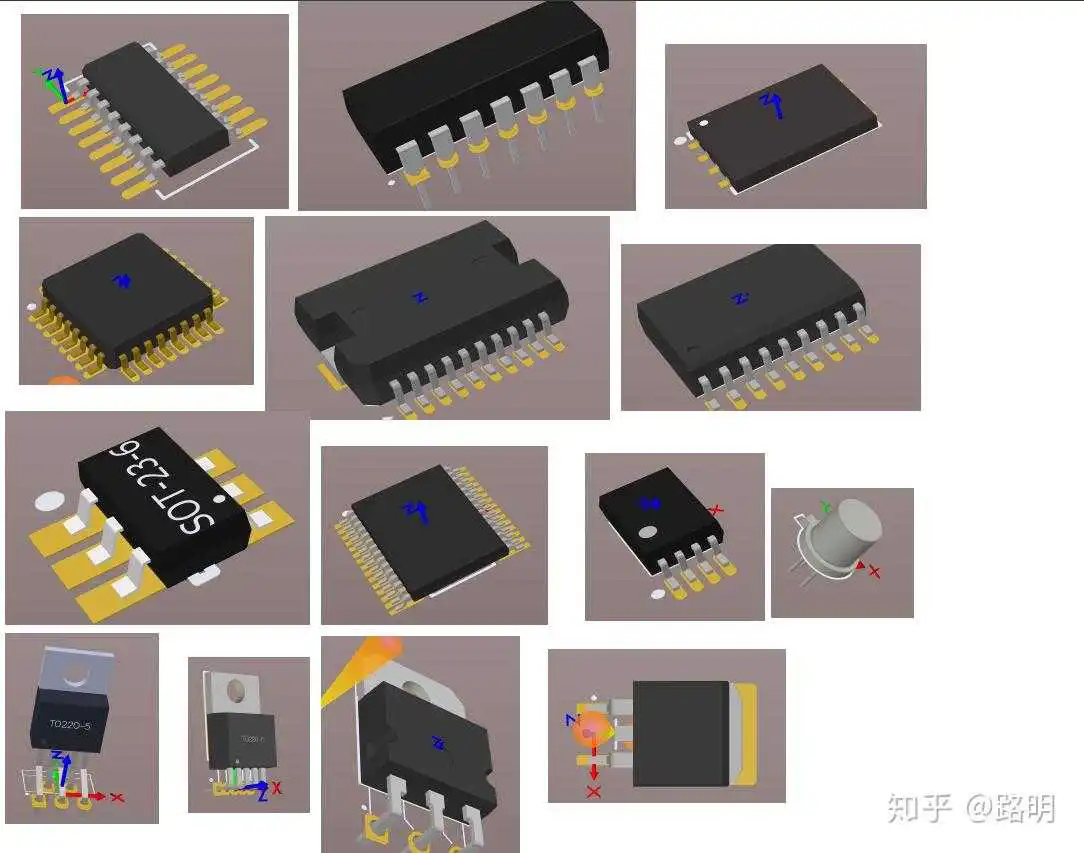

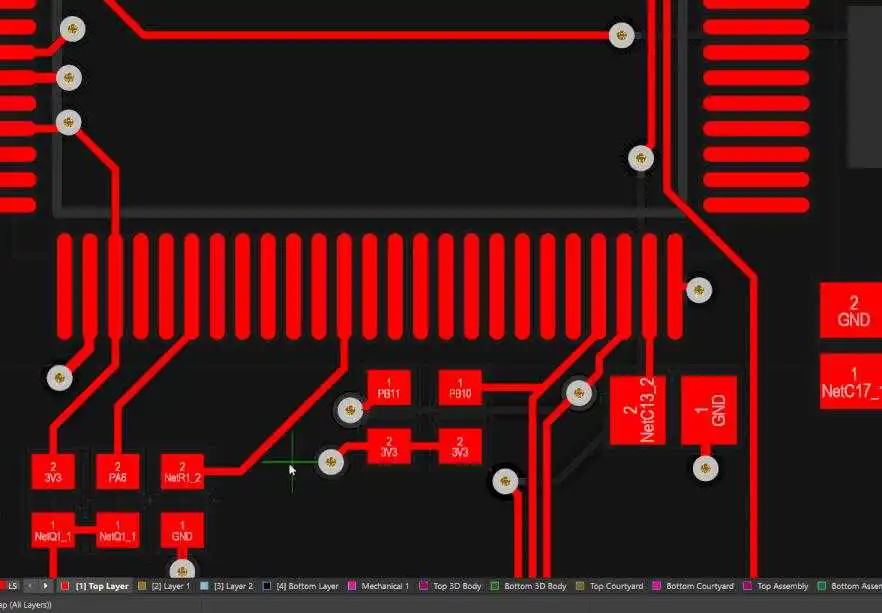

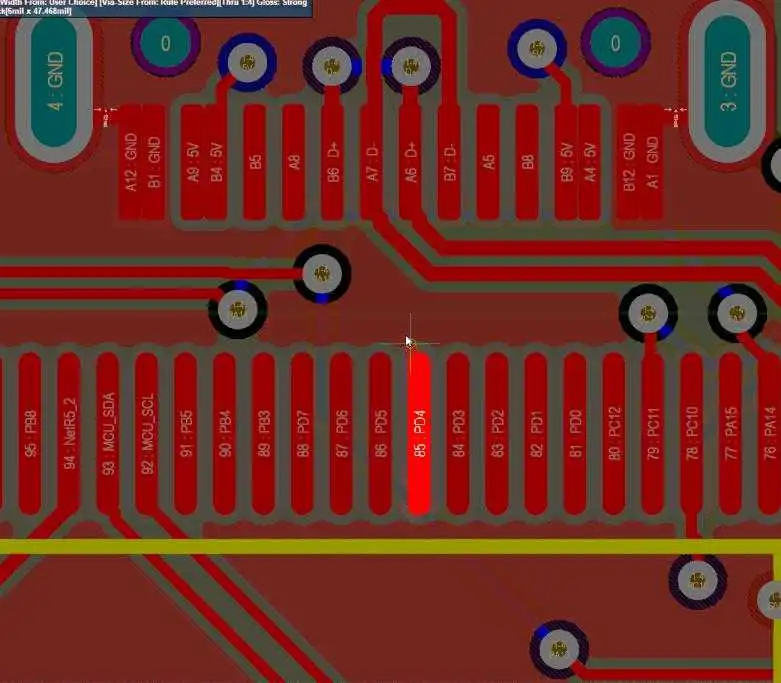

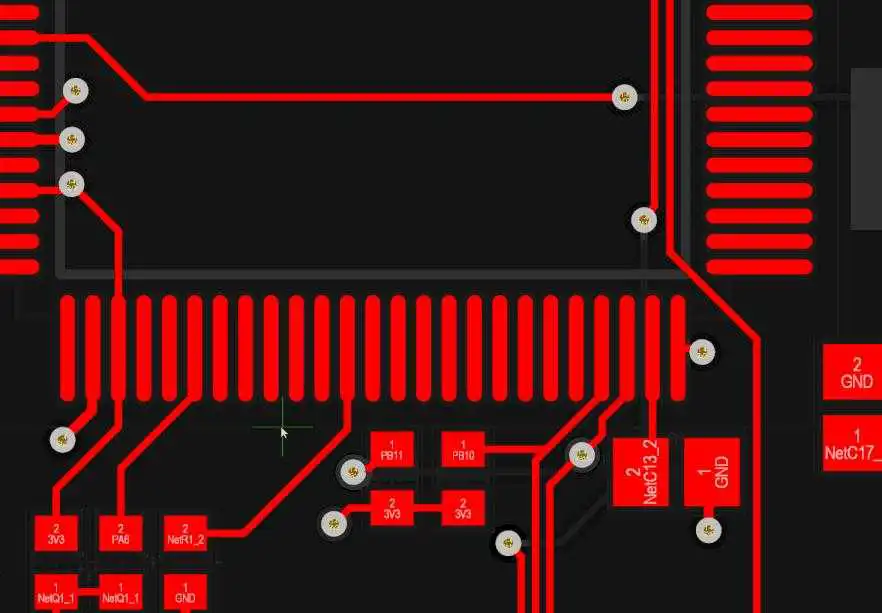

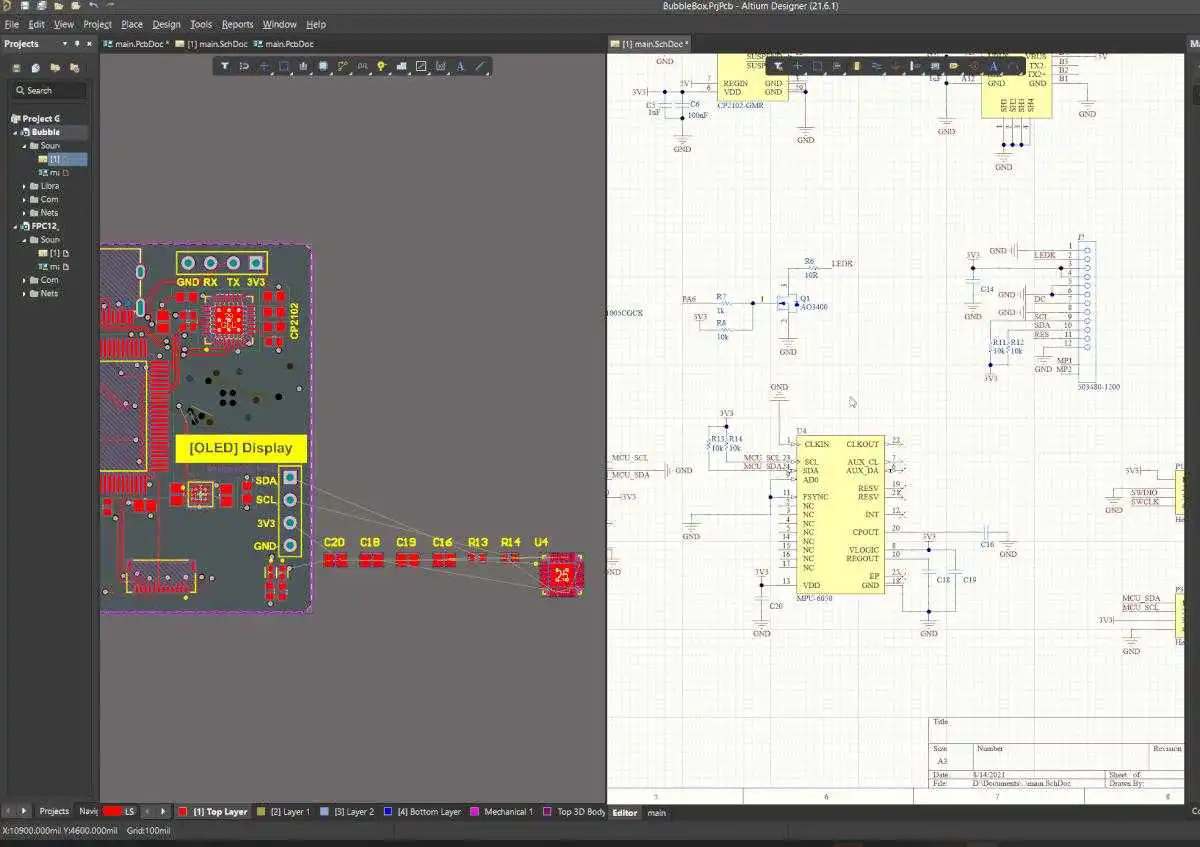

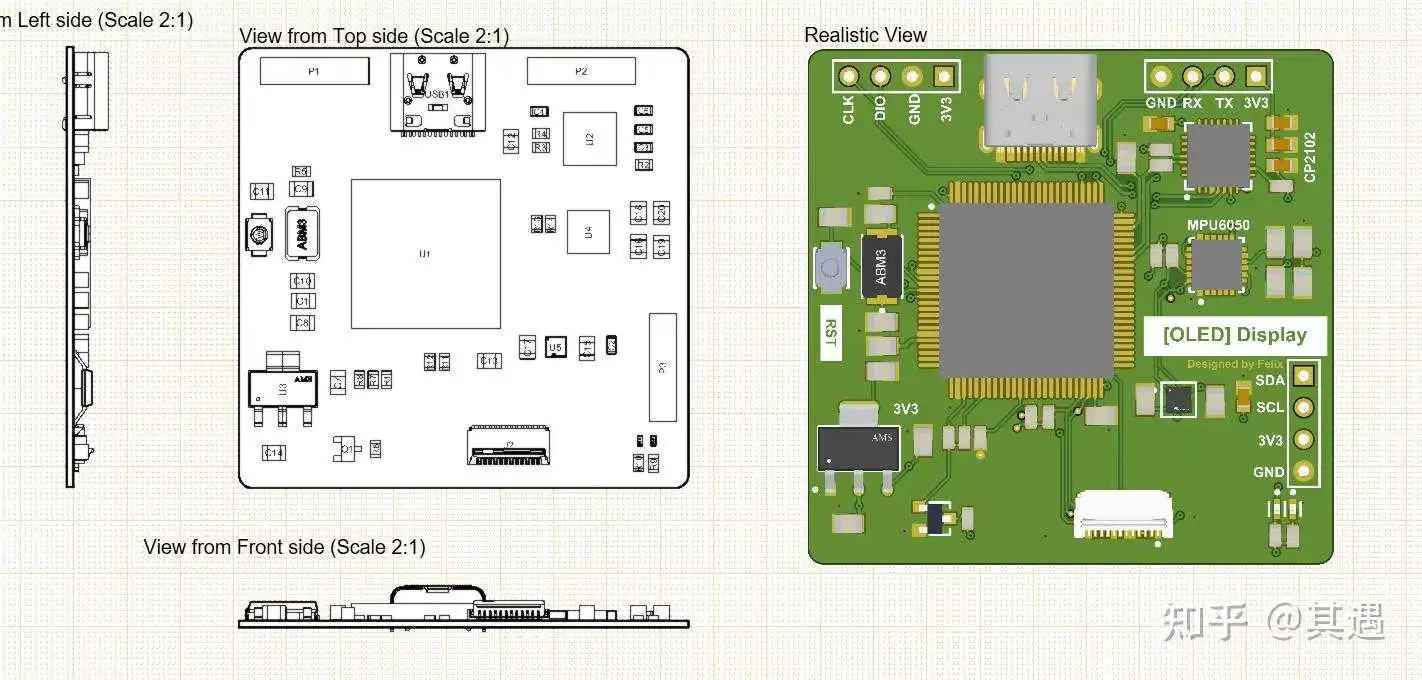

AD里3D像这样,想发给别人看3D效果担心对方没有类似软件可以打开,略棘手。

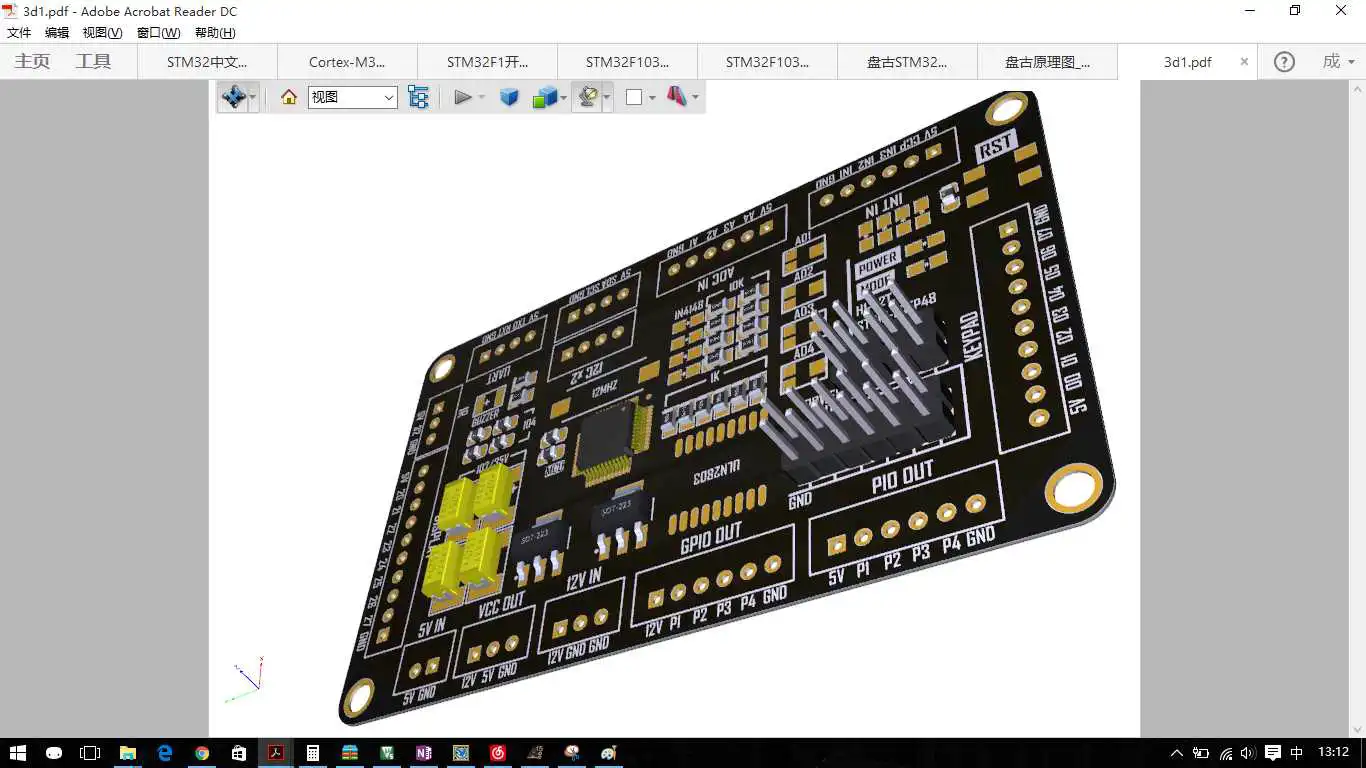

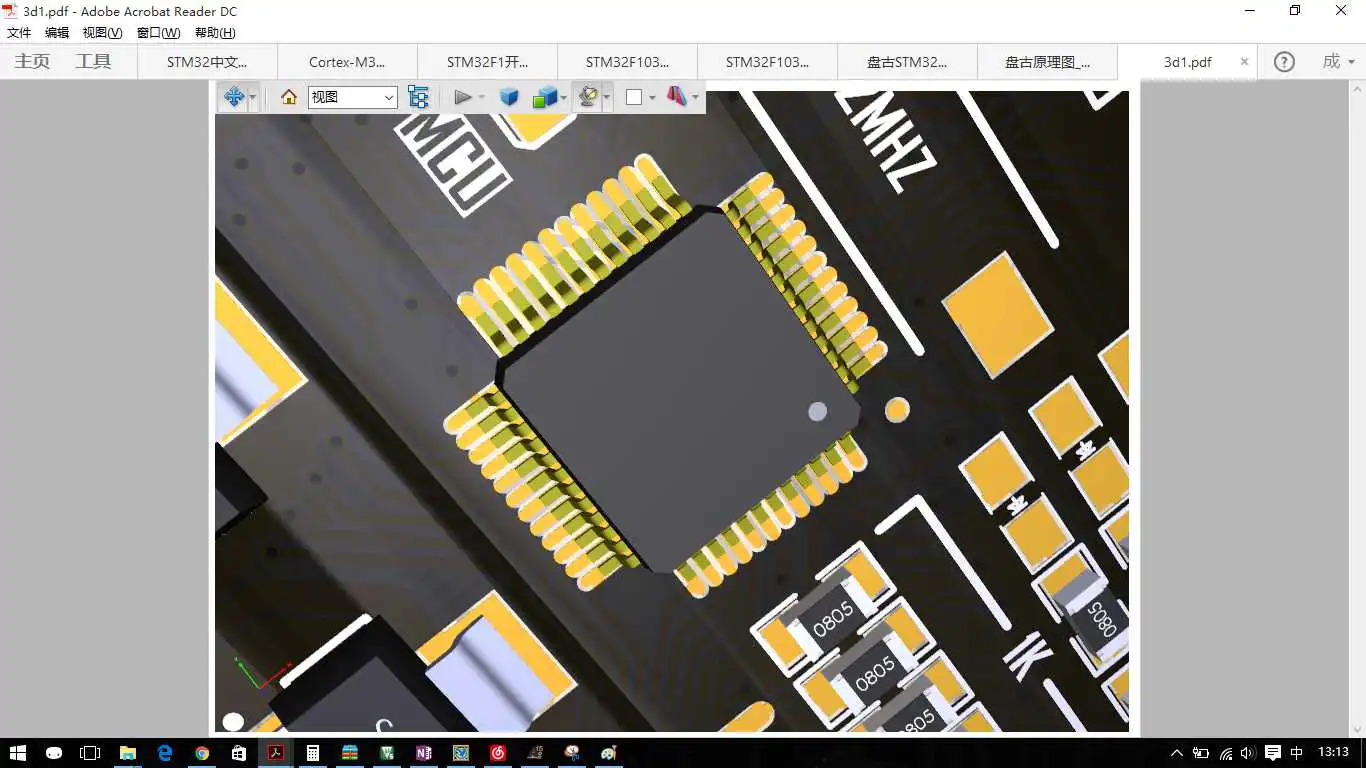

在PDF里面即可任意翻转,放大等。。

一直以为PDF只是“单一式”的阅读工具,没想到居然可以“交互式”的看一个东西。

2月1更:

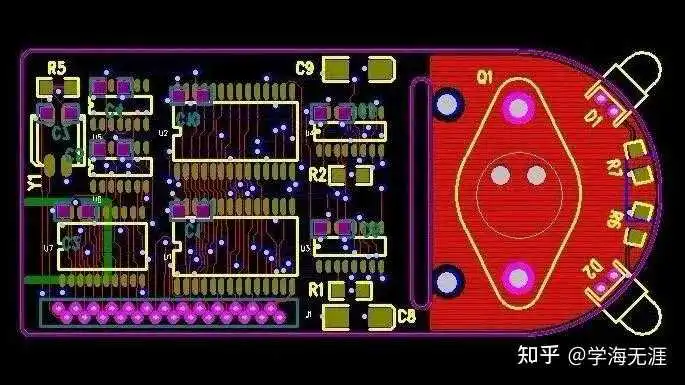

附上实物:

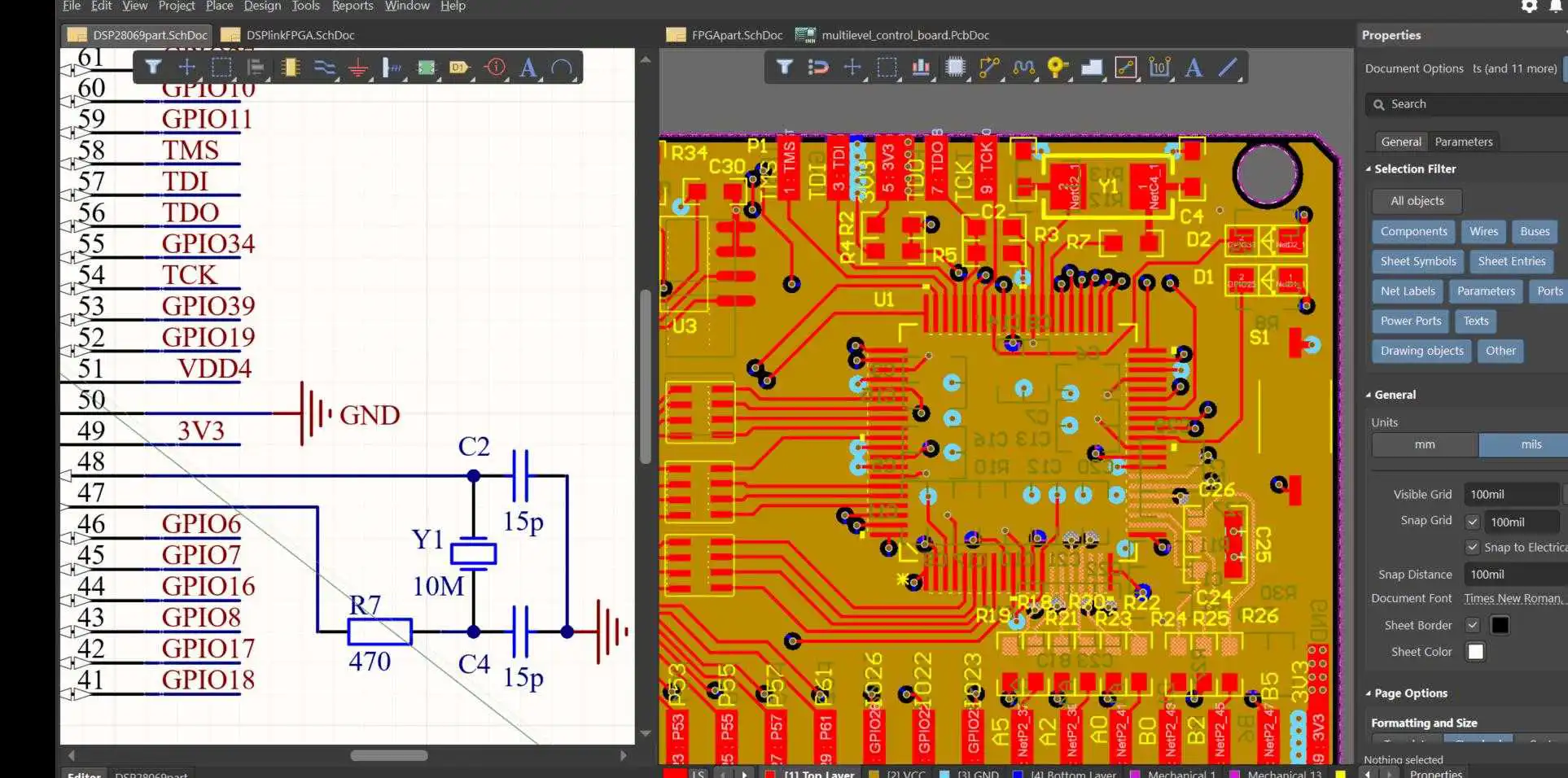

基于Altium Designer绘制印刷电路板浅谈

一、设计流程

(1)原理图设计并仿真

(2)印刷板设计

(3)文件输出

(1)设置原理图纸尺寸

(2)装载或生成元件符号库文件(若系统元件库中没有需要用到的元件符号,则新建元件符号库,并绘制元件符号)

(3)装载或生成封装库文件(若系统封装库中没有需要用到的元件符号,则新建封装库,并绘制元件封装)

(4)放置元件,设置参数并加载元件封装,布局布线,完成电路图的绘制

(5)编译原理图文件并修改

(6)网络报表及其他报表的生成(网络报表是原理图文件向PCB文件转换的桥梁)

(1)载入网络报表,导入到PCB文件中

(2)删除Room并放置坐标原点

(3)设置印刷板尺寸(在Keep-out Layer层用Line画电气边框)

(4)手动布局(一般不使用自动布局)

(5)对布线规则的设置并布线(一般不使用自动布线)

(6)补泪滴(增强焊盘和导线连接的可靠性)

(7)敷铜(增大导电面积,导流能力)

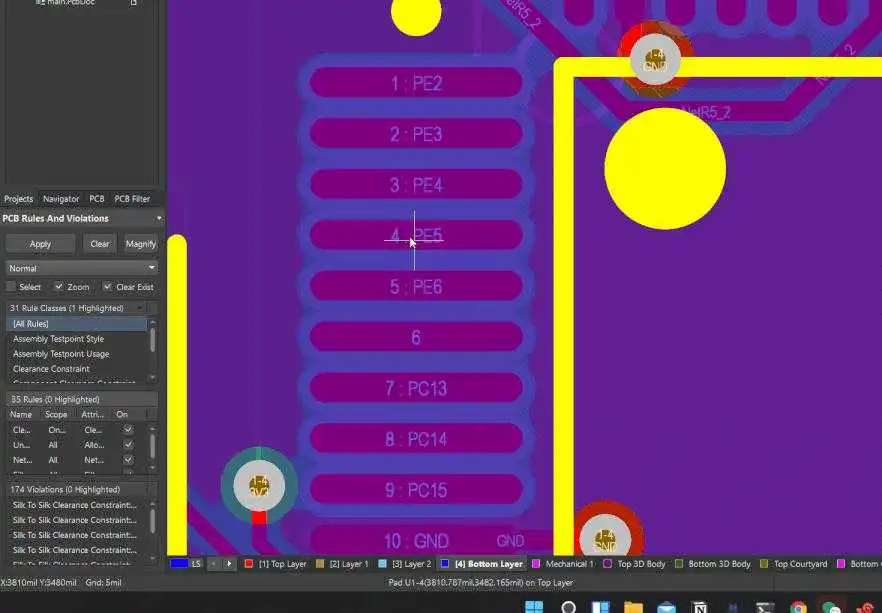

(8)对绘制好的印刷板进行DRC(设计规则检查)校验,若变绿,则说明与规则冲突,对PCB或规则进行修改,直至无误。

(9)保存并输出

二、设计注意事项

(1)顶层(Top Layer)

(2)底层(Bottom Layer)

(3)丝印层(Topover Overlay和Bottom Overlay):显示元件的外形轮廓、编号或放置其他的文本信息。

(4)禁止布线层(Keep-Out Layer):用于定义PCB的电气边界,即限制了布线区域。

(1)网络标号(有相同网络标号的导线具有电气连接意义)。

(2)自动生成流水号(当元件数量众多时省去挨个命名的繁琐)。

(3)群体编辑(当元件数量众多时,可通过寻找相似元件进行群体编辑)。

(4)自动生成元件报表(可生成含元件名称、个数、封装形式等信息的表格供查看,采购等)。

(1)在元件符号库中绘制元件符号时,尽量符合元件功能,增强可读性。

file:///C:\Users\ADMINI~1\AppData\Local\Temp\msohtmlclip1\01\clip_image002.jpg

图1、双管IGBT模块FF75R12YT3元件符号

(2)在元件封装库中绘制元件封装时,保证焊盘尺寸,引脚标号等与官方元件datasheet完全一致(也可使用封装向导,一般焊盘的直径要比引脚直径大0.2~0.4mm)。

file:///C:\Users\ADMINI~1\AppData\Local\Temp\msohtmlclip1\01\clip_image004.jpg

图2、电压霍尔传感器LV25-P元件封装

(3)电路图分区绘制,模块化设计(电源模块、主电路模块、驱动模块、保护模块等)。

(4)电路图绘制尽量保持布局符合功率走向。

file:///C:\Users\ADMINI~1\AppData\Local\Temp\msohtmlclip1\01\clip_image006.jpg

图3、双向DC/DC主电路设计原理图

(1)Electrical(电气规则)

Clearance(安全间距):这里指的间距是走线与走线的最外侧间距,过孔与过孔的最外侧间距。

(2)Routing(走线规则)

Width(走线宽度):这里的Constraints里用来设置走线的最小线宽,参考线宽和最大线宽。

RoutingVias(过孔):在Constraints里设置Via Diameter(过孔外径)和Via Hole Size(过孔内径)最小值、最大值和参考值。

file:///C:\Users\ADMINI~1\AppData\Local\Temp\msohtmlclip1\01\clip_image008.jpg

图4、Design Rules设计

(1)PCB板尺寸尽量符合黄金比例。

(2)遵照“先大后小,先难后易”的布置规则,优先布置重要的单元电路,核心元器件,后放置外围元器件。

(3)参照布置好的原理图,对PCB进行分区布局。

(4)使得电路功率走向尽量与原理图保持一致(一端进,另一端出等)。

(5)元件的排列要便于调试和维修(需调试的元件周围留有足够空间)。

(6)考虑元件的发热问题(例如功率电阻这种发热严重的元件,之间间距应加大)。

(7)使用同一电源的元件尽量放置在一起,以便电源隔离。

(8)表贴元件、直插元件相互之间距离应满足布局规则。

(1)电源、时钟等重要的线应该优先布线,且因为通流量大,布线要求较宽(要求≥20mil,取40mil,其中1mil=0.254mm)。

(2)对重要电路,围绕核心元器件进行布线,信号线通流量小,布线可较细(要求≥10mil,取20mil)。

(3)同一层布线遵循3W规则:为了减少线间窜扰,应保证线间距足够大,当线中心距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。

(4)环路最小原则:信号线与其回路构成回路面积尽可能小,环路面积越小,对外辐射越小,接收外界辐射也越小。

(5)布线拐角模式一般选择45°拐角模式,避免出现同层走线锐角和直角。

(6)不同层导线宜相互垂直,避免相互平行,减少寄生耦合。

(7)尽量少使用过孔,一旦选用过孔,务必处理好过孔与周边各实体的间隙;且根据过孔所在网络制定过孔尺寸(如电源线上的过孔,因需要的载流量大,过孔尺寸也大,选择过孔直径50mil)。

(8)一般对地线进行大面积敷铜处理,以增大地线面积,减小地线阻抗,提高抗干扰能力。

(1)滤波电容问题

① 电源和地出线必先经滤波电容滤波(紧贴电源接入口放置),再走线供电;

② 向芯片供电时,必先经过滤波电容滤波,再接入芯片;

③ 若走线较长,经过过孔之后加滤波电容。

(2)走线宽度问题

在布线之前先计算好线路电流,根据导线载流与线宽的关系,设置布线宽度。

file:///C:\Users\ADMINI~1\AppData\Local\Temp\msohtmlclip1\01\clip_image010.jpg

图5、PCB载流与线宽的关系

三、结束语

原理图作为之后查看电路原理的工具图,要求设计简洁明了,必要时候可文字标识,注释来增强可读性。印刷电路板作为硬件实验平台的基板,在布局布线中充分考虑PCB板与其他实物之间的连接关系,其在机箱中的位置,必要的时候可添加测试孔作为后续做实验时测试点。

谢邀。

喜欢的话请点赞!

如果几乎没有人看,暂时不再更新!码字是个体力活!

先说一下,使用什么软件仅仅是工具而已,都可以设计出好的产品,关键看设计者的思想。

_____

说到设计pcb,在此多说两句。

首先,撇下偏见,有人认为设计pcb是低档活,这个是彻彻底底的抱有歧视的言论。在我们单位,一些硬件工程师,刚带徒弟(我们实行以师徒关系,带新员工)就不再设计pcb了,设计好原理图之后,就彻底扔给徒弟设计,认为pcb仅是个体力活。那样的人永远不会成为高手。

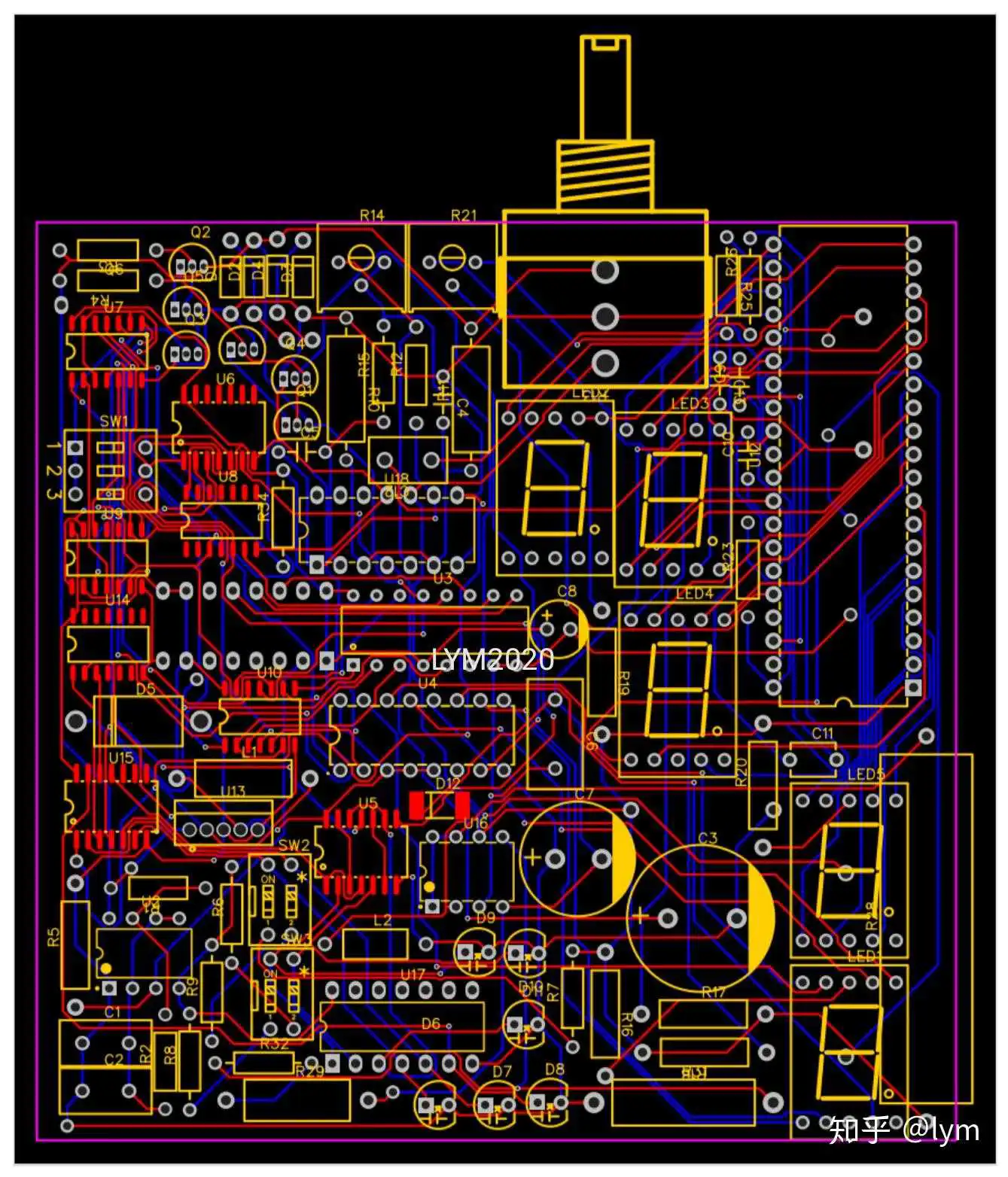

我要说:设计pcb是种艺术。本人是很享受设计pcb这个过程的。或许每个人画出来的板子都能用,但是性能绝对各不相同,好的板子和坏的板子差异很大。怎样设计出好的板子?

主要是设计理念的问题,我们必须掌握正确的设计理念,然后将设计理念正确应用到工程设计中去,转化为真正的产品。所以设计pcb最好的指导书籍就是能使我们掌握设计理念的书籍。在此先给出几个设计理念:

1. 信号完整性

2. 电源完整性

3. 时序完整性

4. 电磁兼容性

5. 可测试行

6. 可制造性

7. 可靠性

先写到这,随后更新。

_____

1. 今天谈一下信号完整性。

推荐书籍:李玉山老师翻译的《信号完整性分析》

信号完整性,就是将发送端信号准确完整的发送到接收端。

在此重点之重点就是掌握传输线的概念。在此抛砖引玉给提示一下。

我们在《电路分析》中总是认为:同一导线上任意两点电压和电流均相等。

现在假设有一个1GHz的正弦波电信号在1m长的双绞线上传输,请问双绞线上每一点电压相等吗?

由于1GHz电信号波长近似为30厘米(暂且认为双绞线塑料层表皮相对介电常数为1,下面类同),当它在1m长的线上传播时,需要接近3个波长长度才能从始端传到末端。大脑想一下水中波纹的传播情况,显然线上不可能每点电压相等,而是像波纹一样分布。

因此,我们不能用电路(集总参数)的理论去分析这种情况,而要用新的不同于电路的理论,即传输线(分布参数)理论分析问题。

此处需要说明:一般线长小于波长1/20时,认为线上任意两点电压相等,可以使用电路理论分析问题,否则使用传输线理论。

为了更好的说明传输线理论,再想象一种情形。

在1m长的双绞线中,始端(源端)发出信号1ns后,电压和电流是怎样分布的?在速度是3*10^8 m/s的情况下,仅仅前进了30cm,并没有到达距离1m远的负载端,有没有电流?有的话电流是哪来的?

今天先说到这,有空继续更新。下面再提几个关键词最好了解一下。

特征阻抗,反射系数,源端匹配,末端匹配,过冲(振铃),CMOS电路输入和输出阻抗特性,串扰,带状线,微带线,趋肤效应,S参数,3w原则等。

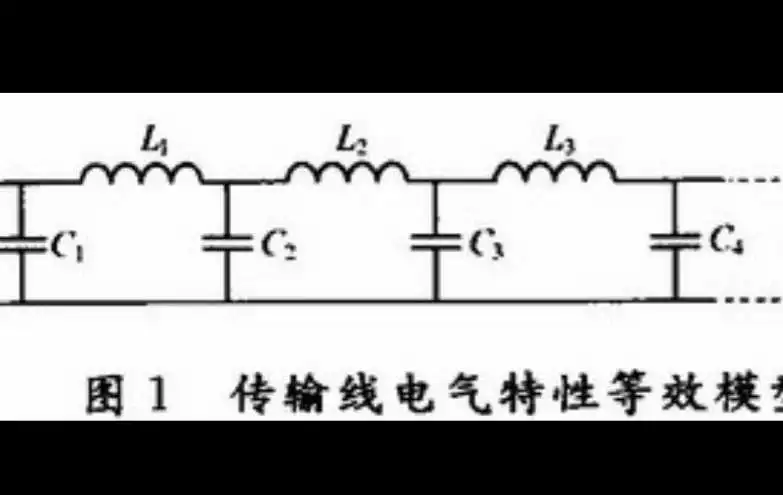

现在需要引入传输线的电路等效模型。既然电路观点认为同一导线上任意两点电流电压相等,那么我们就可以将传输线进行切割,认为是多个一小段一小段的线缆串联连接,当将每一小段分的足够小时,每一小段上电压和电流就是相等的。因此我们就可以在每一个小段上使用电路理论进行分析了。

电路等效模型如下

为了能够看明白电路等效模型,先分析一下电感和电容本质

电容本质是表示电场的存在

电感本质是表示磁场的存在

电信号传输过程实际是电磁波的传输,电磁波既有电场也有磁场,有电场就有电容,有磁场就有电感。因此,我们看到了传输线电路模型是电感加电容。

当交流信号源加载在传输线一侧时,通过电感和电容便有了电流,无需走到负载端即可在返回路径上形成电流。实际上,电流是磁场的旋度源,电荷是电场的散度源,两者同时存在正好符合了电磁波中电场和磁场的传输条件。

走了电压和电流,那么电压除以电流就是阻抗,在此便是传输线的特征阻抗。具体特征阻抗推导请看

https://www.zhihu.com/question/263536553/answer/?utm_source=wechat_session&utm_medium=social]

有了这些知识,我们就可以讨论反射系数和阻抗匹配了。

正如上面所述,传输线中电压V和电流I符合关系

V/I=Z0

其中Z0为传输线的特征阻抗

现在传输线以这个关系将电磁场能量传输了出来,过了一段时间到负载端了。负载阻抗Zl,负载说:对不起,我收下的能量必须符合关系

V/I=Zl

天哪,传输线已经把能量以自己的关系送出来了,但是负载可能不能照单全收,怎么办呢?

传输线只好把一部分能量在返回去,返回去的能量就是反射。如果传输线特征阻抗和负载阻抗相等,就不存在能量返回,就是末端匹配。

信号完整性就说这么多,希望能帮到大家。最后,提一个非常非常重要的概念就是:返回路径。真的很重要,希望大家布线时,时时处处想着她。她就是pcb中的女神!

今天先说到这

_____

今天开始说一下电源完整性

2、电源完整性

电源完整性从两个角度讨论(1)电源完整性产生的原因(2)怎样解决电源完整性

(1)电源完整性产生的原因

两个原因①电源回路存在电感②负载电流是瞬态变化的

先说回路电感,请参考https://www.zhihu.com/question/54976058/answer/?utm_source=wechat_session&utm_medium=social

就是,存在回路就存在磁场,有磁场就有电感

再说负载电流的瞬态变化

现在的数字电路都是CMOS工艺,CMOS器件的静态漏电流很小,但是在电平翻转时的动态电流很大。动态电流包括两部分,一部分是由于输入电压从高电平到低电平或者从低电平到高电平时,会存在中间电平的瞬间,此时上下两个管子均工作在放大区,有经过两个管子从电源到地的电流。另外一部分是由于负载端的电容充放电导致的电流。

因此,在器件工作时钟的上升沿和下降沿会存在较大的动态电流,每次翻转器件数量不同电流也不同。一般除时钟沿外的其他时刻仅消耗漏电流。

瞬态电流经过电流回路电感是有压降,因此出现芯片处的电压不等于电源芯片输出端电压的情况,这便是电源完整性问题的根源。

今天先到这

(2)怎样解决电源完整性

在电源完整性的原因一部分中,我们知道由于电源回路电感的存在,导致电源供应电压不等于芯片用电处电压。

那么怎样才能解决这个问题?唯有减小回路面积,以减小回路电感,进而减小供电线路压降。

但是,整个芯片那么多的电源管脚,怎样可以保证每一个供电管脚均有较小的回路面积呢?

这时候别忘记电容,电容的本事就是储存电荷,每一个电容都可以看做一个小的临时电源,给每一个电源管脚分配一个电容就可以看做每一个管脚分配一个电源,我们就可以减小每一个电源管脚的电源供电回路了。

电容是怎样工作的?

芯片在时钟上升沿和下降沿翻转需要的电流,临时从电容中抽取。在时钟高电平和低电平阶段期间,电容从电源中补充能量,迎接下一次的电流消耗。

我们参观故宫或者古代建筑时,会发现外面都有一口大缸灌满了水,它的作用就是用来应急救火用的。它的作用和咱们的电容是不是很像?

那么需要多大的电容可以满足要求呢?

我们从两个角度考虑

①时域分析

假设芯片瞬间最大电流i,电压允许波动Δv,那么从电容放出电荷等于芯片消耗的电荷,即:

C(Δv)=i(Δt)

此处的(Δt)怎么取?我们知道上升沿和下降沿均消耗电流,所以取芯片工作周期的一半即可

②频域阻抗

时域角度说明了总电容容量,但是对一些细节没有描述,下面我们再从频域考虑电源完整性问题。

频域怎么看问题呢?

我们将频率为w0的正弦电压u加到电源上,电源会输出一个同样频率的电流i,那么就得到频率w0时的电源阻抗

Z(w=w0)=u╱i

同样,芯片消耗的的特定频率w0的电流i(w=w0)流经同样的回路,将感受到同样的回路阻抗Z(w=w0),此时将产生一个压降

U(w=w0)=i(w=w0)×Z(w=w0)

但是,实际上我们并不能得到芯片在电源上对电压的纹波频域特性要求和电流的频域特性

怎么办?怎么办?难道频域分析半天没有用了?

不,这些难不倒我们的工程师

我们使用最坏情况进行分析

假如允许最大纹波电压(Δu)max,瞬间消耗最大电流imax,那么令

U(w)=(Δu)max

i(w)=imax

此时,可以算出Z(w)=U(w)╱i(w)

在设计过程中,只要频域阻抗低于Z(w)就可以保证,电源纹波满足芯片要求了

频域设计方法由于使用了最坏情况分析法,所以设计裕度非常大。

实际使用频域阻抗设计要求非常严格,有时是不可能满足的。这个方法给我们提供了一个角度看问题,具体设计出来还得进行测试。

以上,将理论讲完了,随后更新PCB设计过程中的注意事项。

刚刚画完人生第一块板子,从小白入门,就用的立创eda,太好上手了。 虽然仿真库不太全,但是原件库是真的全,并且还有原件价格标注,bom里面还能直接购买,一站式配齐。最主要的像一些特殊的开关,电阻等等自带根本不用手动去画,而且所有原件一点击就能看到官方技术手册,对于小白的我实在太友好了,省下了很多时间。仿真跑不了,不过自动布线和交叉选择是特别特别方便,还能自动导出制板文件。虽然我的板子太复杂,板子很大几率是会出问题的,不过嘉立创一次下单仅5元,太便宜了,多下几次也不心疼。 最后就是哪天立创的股票上市了,一定挺醒我一起发财。

网上类似的教学视频挺多的,这里推荐一个吧。凡亿教育的郑振宇,讲的一个stm32四层板的pcb设计,b站上有免费视频。这个视频比较适合小白,讲的比较详细易懂。

Ps:这个视频有个特点,老师会自己故意弄些经常会遇到的问题出来,装作自己什么都不知道,然后再教你怎么解决。这种明知道是自己故意而为之,却装作一脸茫然举足无措的样子,还真是有点可爱呢。。(希望郑老师看不到)

当然可以,国内优秀的,应该也是唯一的电子EDA设计软件。新入职的公司就在用LCEDA,以前被AD骚扰的不行。之前的公司招的应届生也在用LCEDA呢。

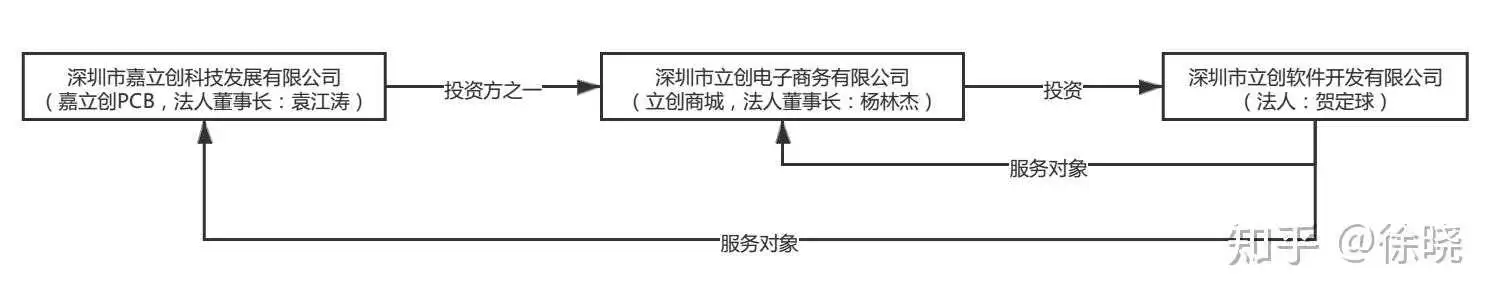

正好以前和LCEDA的创始人,现在的立创商城副总老贺吃过饭,知道他们最关键时期的一些事情,拿出来聊聊。

第一次知道这个软件是在2015年,那个时候叫做EasyEDA(现在国外仍然是这个域名Online PCB design & circuit simulator),当时创始人老贺(贺定球,请原谅我第一次见到这个名字内心哈哈哈~)还在为产品宣传和寻找投资而烦恼。那个时候老贺已经全职创业几年了,并且把公司从杭州搬到了深圳,并且已经有了不少海外用户,而且是美国用户比较多,毕竟那边工程师的版权意识和尝鲜意识都强一些,不好意思用盗版和尝试新鲜事物使EasyEDA在美国还设了办事处(貌似就是有个外国朋友帮忙)。

那个时候在一电子论坛老贺私信找人试用EasyEDA,恰好私聊找到了我,试用之下给我的感觉是惊艳——在这个年代里,有这样的技术能力不去赚钱搞这种基础性软件开发,而且真的挺好用呀!

于是在论坛里写了个推荐帖:

因为这个推荐帖,老贺请我吃了个饭,恩肯德基,当时都是创业者,也都是真的都没钱。老贺以前是杭州一所电子类高校的模电老师,后来吹了个做EDA的牛,就自己卖了杭州的房子出来创业了。彼时EasyEDA的处境也是十分艰难的,老贺跑北京上海,见各种投资人,而那些投资人并不了解这是个什么产品,只是依照互联网的惯例计算流量、用户数量、日活啥的。费老劲才融个几百万羊币。艰难的活着。

说起来我发的帖子成了接下来EasyEDA的很多事情都的导火索。只能是导火索,因为老贺自己迟早会走到这一步,我的帖子只是让一些事提前发生了而已(也就提前个一两天吧)。

帖子所在的电子论坛里面很多人看到后都去试用了一下,行业内的工程师们都很感慨,终于有了国产的电子EDA软件。而嘉立创PCB的老总袁江涛先生也在论坛里,再加上论坛坛主的撮合,最终EasyEDA委身下嫁立创商城。

这里要注意一下,嘉立创PCB,立创商城和LCEDA三者之间的关系。

嘉立创就是最近被PCB制版行业所厌恶的企业,因为对小批量客户进行拼板打样的操作导致被很多同行中伤诋毁,记得2011年在北京的时候PCB打样找沧州的公司,两层半一次大概也得300+的打样费用,当时淘宝的深圳打样貌似是100多(拼板),后来嘉立创开始做这一块拼板打样的业务,逐渐把价格拉到了现在普通两层板打样20块钱……(这TMD直接让同行没钱挣呀)

嘉立创的老总袁江涛先生领头投资成立了立创商城,以前大家买正品元器件大都上贸泽这一类的外国网站,淘宝虽然也有,但是买到汕头货(翻新、假货)的概率很大。与立创同时期的还有华强等一些网站,但是立创价格、页面设计上更友好一些。

自从立创商城收购了老贺的EasyEDA团队,页面友好度、页面刷新速度等都有了显著提升,毕竟敢自己出来创业的,技术实力都是相当彪悍的。但是到目前为止立创商城的元件参数搜索功能仍然不足以和贸泽相比,当然这项工作不单纯是软件功能问题,需要大量有经验的工程师去告知哪一类元件大家会关注哪些参数。

而且嘉立创的全自动下单系统,明显也是出于EasyEDA团队之手,其实嘉立创的PCB打样都打造成典型的工业4.0模板了。

得知EasyEDA被立创商城收购以后,个人心理不知道是该祝福老贺,还是遗憾这样一款重量级的基础应用软件没办法自己生存下去。

言归正传,说到使用LCEDA,因为自己习惯用AD,所以并没有马上迁移到LCEDA,使用仅限于后来申请专利的电路图,毕竟用AD有盗版法律风险。

但是吧,事物是发展的,LCEDA自从被立创商城收购以后,把立创商城所售卖的元件都做成了原理图和PCB的封装库文件,这一下可方便太多了。以前用新的电子元件画原理图PCB需要自己画封装,现在只需要去LCEDA上,把封装导出来就可以了,LCEDA兼容AD的,可以把文件导出成AD格式。

接下来就是LCEDA的推广了,借助立创商城举办的各种赛事,以及在高校的推广,LCEDA正在被新生代的工程师们接受者,那些声称LCEDA火不了的工程师,大概率会像二十年前手绘PCB和十年前用protel99的老师傅们一样,逐渐被新生事物所取代。毕竟这才是客观规律。

AD在国内不停的骚扰各个电子公司(打电话、发律师函),但是一套AD要十几万呢,用LCEDA就很好了,可以免费,四层板以下无压力,适合创业公司和小型团队。有些人会关注保密,实际上单纯的PCB保密意义并不大,毕竟别人不知道你的用途,而行业内真正需要这些秘密的人,买来拆开看下就好了,超板费又不贵。

至于复杂的,需要采用Candece完成的工程项目,LCEDA也能完成,只不过现在易用性上面可能还不如Candece,新生事物还是要逐渐完善嘛。

在国家十四五战略规划中,国产EDA软件已经列入了重点支持领域,相信上面的人会擦亮眼睛的,已经被大众接受的国产EDA软件中,LCEDA应该是首屈一指的。其重要意义并不亚于国产办公软件WPS,不知道后面国企、央企是否要进行采购呢。现在的LCEDA客户端做的很好,也支持私有化部署,路程是艰辛的,前景是光明的。

自己所在的传感器领域能看到太多国内力所不及的领域,也看到很多民间创业者的有心无力的在这些领域缓慢前行,他们不是互联网领域,不是资本的宠儿;他们也不是五道口技校的教授,光环加持,有个想法就能有人奉上几千万的启动资金;他们更不是国企央企的亲儿子干儿子,一年拿两个项目,不论成与不成都能拿几个亿养活自己。但是,他们是真正的创业者者,真正的行业专家,真正在一些细分领域,向着世界顶级品质的产品慢慢前行,他们中相当一部分已经在海外市场拿到了属于自己的份额,而不是用从纳税人那里拿到的补贴去向自己不懂的领域交学费。同时以此帖,向这些真正的创业者们致敬。

104条 PCB 布局布线技巧问答,助你画板无忧!

现在,虽然有很多软件可以实现PCB自动布局布线。但是随着信号频率不断提升,很多时候,工程师需要了解有关PCB布局布线的基本的原则和技巧,才可以让自己的设计完美无缺。

下面涵盖了PCB布局布线的相关基本原理和设计技巧,以问答形式解答了有关PCB布局布线方面的疑难问题。

PCB布局布线的相关基本原理和设计技巧

学海无涯:入行电子硬件工程师的,看看这篇吧,保你赚到!

1、[问] 高频信号布线时要注意哪些问题?

[答 ]

- 信号线的阻抗匹配;

- 与其他信号线的空间隔离;

- 对于数字高频信号,差分线效果会更好。

2、[问] 在布板时,如果线密,过孔就可能要多,当然就会影响板子的电气性能,请问怎样提高板子的电气性能?

[答] 对于低频信号,过孔不要紧,高频信号尽量减少过孔。如果线多可以考虑多层板。

3、[问] 是不是板子上加的去耦电容越多越好?

[答] 去耦电容需要在合适的位置加合适的值。例如,在你的模拟器件的供电端口就进加,并且需要用不同的电容值去滤除不同频率的杂散信号。

4、[问] 一个好的板子它的标准是什么?

5、[问] 通孔和盲孔对信号的差异影响有多大?应用的原则是什么?

[答] 采用盲孔或埋孔是提高多层板密度、减少层数和板面尺寸的有效方法,并大大减少了镀覆通孔的数量。

但相比较而言,通孔在工艺上好实现,成本较低,所以一般设计中都使用通孔。

6、[问] 在涉及模拟数字混合系统的时候,有人建议电层分割,地平面采取整片敷铜,也有人建议电地层都分割,不同的地在电源源端点接,但是这样对信号的回流路径就远了,具体应用时应如何选择合适的方法?

[答] 如果你有高频>20MHz信号线,并且长度和数量都比较多,那么需要至少两层给这个模拟高频信号。一层信号线、一层大面积地,并且信号线层需要打足够的过孔到地。这样的目的是:

- 对于模拟信号,这提供了一个完整的传输介质和阻抗匹配;

- 地平面把模拟信号和其他数字信号进行隔离;

- 地回路足够小,因为你打了很多过孔,地又是一个大平面。

7、[问] 在电路板中,信号输入插件在PCB左边沿,mcu在靠右边,那么在布局时是把稳压电源芯片放置在靠近接插件(电源IC输出5V经过一段比较长的路径才到达MCU),还是把电源IC放置到中间偏右(电源IC的输出5V的线到达MCU就比较短,但输入电源线就经过比较长一段PCB板)?或是有更好的布局?

[答] 首先你的所谓信号输入插件是否是模拟器件?如果是是模拟器件,建议你的电源布局应尽量不影响到模拟部分的信号完整性.因此有几点需要考虑:

- 首先你的稳压电源芯片是否是比较干净,纹波小的电源.对模拟部分的供电,对电源的要求比较高;

- 模拟部分和你的MCU是否是一个电源,在高电路的设计中,建议把模拟部分和数字部分的电源分开;

- 对数字部分的供电需要考虑到尽量减小对模拟电路部分的影响。

8、[问] 在高速信号链的应用中,对于多ASIC都存在模拟地和数字地,究竟是采用地分割,还是不分割地?既有准则是什么?哪种效果更好?

[答] 迄今为止,没有定论。一般情况下你可以查阅芯片的手册。

9、[问] 何时要考虑线的等长?如果要考虑使用等长线的话,两根信号线之间的长度之差不能超过多少?如何计算?

[答] 差分线计算思路:如果你传一个正弦信号,你的长度差等于它传输波长的一半是,相位差就是180度,这时两个信号就完全抵消了。

所以这时的长度差是值。以此类推,信号线差值一定要小于这个值。

10、[问] 高速中的蛇形走线,适合在那种情况?有什么缺点没,比如对于差分走线,又要求两组信号是正交的?

- 如果蛇形走线在计算机板中出现,其主要起到一个滤波电感和阻抗匹配的作用,提高电路的抗干扰能力。计算机主机板中的蛇形走线,主要用在一些时钟信号中,如PCI-Clk,AGPCIK,IDE,DIMM等信号线。

- 若在一般普通PCB板中,除了具有滤波电感的作用外,还可作为收音机天线的电感线圈等等。如2.4G的对讲机中就用作电感。

- 对一些信号布线长度要求必须严格等长,高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据)。

如INTELHUB架构中的HUBLink,一共13根,使用233MHz的频率,要求必须严格等长,以消除时滞造成的隐患,绕线是惟一的解决办法。一般要求延迟差不超过1/4时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽、线长、铜厚、板层结构有关,但线过长会增大分布电容和分布电感,使信号质量有所下降。

所以时钟IC引脚一般都接;" 端接,但蛇形走线并非起电感的作用。相反地,电感会使信号中的上升沿中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距少是线宽的两倍。

信号的上升时间越小,就越易受分布电容和分布电感的影响。 - 蛇形走线在某些特殊的电路中起到一个分布参数的LC滤波器的作用。

11、[问]在设计PCB时,如何考虑电磁兼容性EMC/EMI,具体需要考虑哪些方面?采取哪些措施?

另外,注意高频信号电流之回流路径使其回路面积尽量小(也就是回路阻抗loop impedance 尽量小)以减少辐射, 还可以用分割地层的方式以控制高频噪声的范围,适当的选择PCB 与外壳的接地点。

12、[问] 请问射频宽带电路PCB的传输线设计有何需要注意的地方?传输线的地孔如何设置比较合适,阻抗匹配是需要自己设计还是要和PCB加工厂家合作?

[答] 这个问题要考虑很多因素.比如PCB材料的各种参数,根据这些参数建立的传输线模型,器件的参数等。

阻抗匹配一般要根据厂家提供的资料来设计。

13、[问] 在模拟电路和数字电路并存的时候,如一半是FPGA或单片机数字电路部分,另一半是DAC和相关放大器的模拟电路部分。各种电压值的电源较多,遇到数模双方电路都要用到的电压值的电源,是否可以用共同的电源,在布线和磁珠布置上有什么技巧?

[答] 一般不建议这样使用.这样使用会比较复杂,也很难调试。

14、[问] 您好,请问在进行高速多层PCB设计时,关于电阻电容等器件的封装的选择的,主要依据是什么?常用那些封装,能否举几个例子。

[答] 0402是手机常用;0603是一般高速信号的模块常用;依据是封装越小寄生参数越小,当然不同厂家的相同封装在高频性能上有很大差异。

15、[问] 一般在设计中双面板是先走信号线还是先走地线?

[答] 这个要综合考虑.在首先考虑布局的情况下,考虑走线。

16、[问] 在进行高速多层PCB设计时,应该注意的问题是什么?能否做详细说明问题的解决方案。

[答] 应该注意的是你的层的设计,就是信号线、电源线、地、控制线这些你是如何划分在每个层的。

17、[问] 请问具体何时用2层板,4层板,6层板在技术上有没有严格的限制?(除去体积原因)是以CPU的频率为准还是其和外部器件数据交互的频率为准?

[答] 采用多层板首先可以提供完整的地平面,另外可以提供更多的信号层,方便走线。

18、[问] PCB布线对模拟信号传输的影响如何分析,如何区分信号传输过程中引入的噪声是布线导致还是运放器件导致。

19、[问] 近我学习PCB的设计,对高速多层PCB来说,电源线、地线和信号线的线宽设置为多少是合适的,常用设置是怎样的,能举例说明吗?例如工作频率在300Mhz的时候该怎么设置?

20、[问] 请问怎样的布局才能达到的散热效果?

- 电子元器件的发热;

- P c B本身的发热;

- 其它部分传来的热。

在这三个热源中,元器件的发热量,是主要热源,其次是PCB板产生的热,外部传入的热量取决于系统的总体热设计,暂时不做考虑。

那么热设计的目的是采取适当的措施和方法降低元器件的温度和PCB板的温度,使系统在合适的温度下正常工作。

21、[问] 可否解释下线宽和与之匹配的过孔的大小比例关系?

[答] 这个问题很好,很难说有一个简单的比例关系,因为他两的模拟不一样。一个是面传输一个是环状传输。

可以在网上找一个过孔的阻抗计算软件,然后保持过孔的阻抗和传输线的阻抗一致就行。

22、[问] 在一块普通的有一MCU控制的PCB电路板中,但没大电流高速信号等要求不是很高,那么在PCB的四周外的边沿是否铺一层地线把整个电路板包起来会比较好?

23、[问]

1)我知道AD转换芯片下面要做模拟地和数字地的单点连接,但如果板上有多个AD转换芯片的情况下怎么处理呢?

2)多层电路板中,多路开关(multiplexer)切换模拟量采样时,需要像AD转换芯片那样把模拟部分和数字部分分开吗?

[答]

- 几个ADC尽量放在一起,模拟地数字地在ADC下方单点连接;

- 取决于MUX与ADC的切换速度,一般ADC的速度会高于MUX,所以建议放在ADC下方。

24、[问] 在常规的网络电路设计中,有的采用把几个地连在一起,有这样的用法吗?为什么?谢谢!

25、[问] PCB中的模拟部分和数字部分、模拟地和数字地如何有效处理?

[答] 模拟电路和数字电路要分开区域放置,使得模拟电路的回流在模拟电路区域,数字的在数字区域内,这样数字就不会影响到模拟。

26、[问] 模拟电路和数字电路在PCB板设计时,对地线的设计有哪些不同?需要注意哪些问题?

27、[问] 去耦电容一般有两个,0.1和10的,如果面积比较紧张的情况话,如何放置两个电容,哪个放置背面好些?

28、[问] 请问老师,射频电路中,经常会出现IQ两路信号,请问这两根线的长度是否需要一样?

29、[问] 高频信号电路的设计与普通电路设计有什么不同吗?能以走线设计为例简单说明一下吗?

30、[问] 高速PCB,布线过程中过孔的避让如何处理,有什么好的建议?

31、[问] PCB板设计中电源走线的粗细如何选取?有什么规则吗?

32、[问] 数字电路和模拟电路在同一块多层板上时,模拟地和数字地要不要排到不同的层上?

33、[问] 一般数字信号传输时多几个过孔比较合适?(120Mhz以下的信号)

34、[问] 在即有模拟电路又有数字电路的电路中,PCB板设计时如何避免互相干扰问题?

[答] 模拟电路如果匹配合理辐射很小,一般是被干扰。干扰源来自器件、电源、空间和PCB;数字电路由于频率分量很多,所以肯定是干扰源。

35、[问] 对于高速线路板,到处都可能存在寄生参数,面对这些寄生参数,我们是各种参数然后再来消除,还是采用经验方法来解决?应该如何平衡这种效率与性能的问题?

36、[问] 多层板布局时要注意哪些事项?

37、[问] 如何避免高速信號的crosstalk?

38、[问] 请问在多层板设计中经常会用到电源平面,可是在双层板中需要设计电源平面吗?

39、[问] PCB板的厚度对电路有什么影响吗?一般是如何选取的?

40、[问] 地平面可以使信号回路,但是也会和信号线产生寄生电容,这个应该怎么取舍?

41、[问] LDO输出当做数字电源还是模拟电源意思是数字跟模拟哪个先接电源输出好?

42、[问] 请问应该在模拟Vcc和数字Vcc之间用磁珠,还是应该在模拟地和数字地之间用磁珠呢?

43、[问] LVDS等差分信号线如何布线?

44、[问] 一个好的PCB设计,需要做到自身尽量少的向外发射电磁辐射,还要防止外来的电磁辐射对自身的干扰,请问防止外来的电磁干扰,电路需要采取哪些措施呢?

45、[问] 采用高时钟频率的快速集成电路芯片电路,在PCB板设计时如何来解决传输线效应的问题?

[答] 这个快速集成电路芯片是什么芯片?如果是数字芯片,一般不用考虑。

46、[问]在一个多层的PCB设计中,是否还需要覆铜呢?如果覆铜的话应该将其连接到哪一层?

47、[问] 在高速多层PCB设计时,进行阻抗仿真一般怎么进行,利用什么软件?有什么要特别注意的问题吗?

48、[问] 有些器件的引脚较细,但是PCB板上走线较粗,连接后会不会造成阻抗不匹配的问题?如果有该如何解决?

49、[问] 差分线一般都需要等长如果实在在LAYOUT中有困难实现,是否有其他补救措施?

50、[问] 在用万用表测量芯片的模拟地与数字地接口的时候是导通的,这样模拟地域数字地不就是多点连接了吗?

[答] 芯片内部的地管脚都是连接在一起的。但是在PCB板上仍然需要连接。

51、[问] 由于受到板子尺寸的限制,我的电路板采用两面贴片焊接芯片,板子上走了很多的过孔,信号线也走在附近,这样走线会对信号产生干扰吗?

52、[问] 数字线在考虑要不要做阻抗匹配时,是看信号传出至反射回来时,总时间是否超过上升沿的20%,若超过则需阻抗匹配。请问模拟线要不要阻抗匹配?怎样考虑?

53、[问] 关于完整的地平面,在使用AD/DA芯片的板子上,如果层数比较多,可以提供一个完整的模拟地和一个完整的数字地;也可以在这两层地平面上都分别划分模拟地,数字地。二者孰优孰劣?

54、[问] 用磁珠或MECCA连接数字、模拟地时,是利用其频率特性,使数字地中高频成分不影响模拟地,同时保证二者电平相等。那么,0ohm电阻连接数字、模拟地有什么作用,有时还只用一小块铜连接,能分析一下吗?

[答] 磁珠的等效电路相当于带阻限波器,只对某个频点的噪声有显著抑制作用,使用时需要预先估计噪点频率,以便选用适当型号。

对于频率不确定或无法预知的情况,磁珠不合。0欧电阻相当于很窄的电流通路,能够有效地限制环路电流,使噪声得到抑制。

电阻在所有频带上都有衰减作用(0欧电阻也有阻抗),这点比磁珠强。铜皮类似于0ohm电阻。)

55、[问] 如何避免布线时引入的噪声?

56、[问] PCB如何预防PWM等突变信号对模拟信号(如运放)产生的干扰,又如何进行测试这种干扰(辐射干扰或传导干扰)的大小?除布局布线需要注意外,有无其他方法来进行抑制(除屏蔽的手段)?

[答] 要从运放的几个接口入手,输入端要防止空间耦合干扰和PCB串扰(布局改善);电源需要不同容值去耦电容。测试可以用示波器的探头测试上面说的位置,判断出干扰从何而来。

57、[问] 请问,在电路板中,一个ARM或者FPGA经常会向外连接很多RAM,FLAH这样的器件,请问这些主芯片与这些存储器之间的连线需要注意什么,过孔的数目有什么限制么?数字信号中常用的过孔孔径大小是多少?过孔孔径的大小对信号的影响大么?

58、[问] 请问在布双面板(高频是)的时候,顶层地和底层地相连时的过孔也是越少越好吗?那么要怎么放过孔比较合理呢?

59、[问] LVDS信号布线应该注意哪些?如何布线?

60、[问] 请问数据线并行布线是不是为了相互干扰?

61、[问] 在一块4层板,布有一整个采集系统,有模拟放大、数字采集、MCU。布好后,如何测量此系统的输入阻抗,如何做到系统的输入阻抗和传感器匹配,如何匹配,有没有相关的设计原则?

62、[问] 经常会看到PCB板上有很多地孔,这些地孔是越多越好吗?有什么规则吗?

63、[问] 在多层板布线的时候难免会有跨平面的现象。我们现在的做饭是在割平面时尽量优先照顾到差分线不跨平面。但有以为老师的说法是单端的不能跨,差分的反倒没那么严格。请教下老师对此的看法?

64、[问] 在高速多层PCB设计时,数字地和模拟地怎么区分?是根据器件的数据手册中说明的进行连接吗?

65、[问] 对PCB走线的熔断电流如何考虑??PCB走线多大电流时会熔断,和哪些因素有关?

66、[问] 请问,在信号输入输出接口和电源输入接口等方面需要做哪些保护?电源为220V输入转直流时,在实际应用时,需要采取哪些防护措施?

67、[问] 见PCB板的布线折弯时有45度角和圆弧两种,有何优缺点,怎么选择?

68、[问] 在高频走线中如果尺寸受限,常用的走线方法或者说合理的走线方法有那些?比如说蛇形走线,可以吗?

69、[问] 请问在使用仪表放大器时关键的输入型号,我在器件层其周围还有必要覆铜吗,我在器件的底层已经覆铜了。还有仪表放大器的反馈电阻我是用直插的,引线就长了,换成贴片的电阻温漂和就达不到要求,请问该怎样处理?

70、[问] PCB软件可以自动布线,但器件的位置布局是不是得手动放置?

71、[问] 在做PCB板制板时,PCB选材有没有什么特殊的规定或是一般如何选材?我现在在制作高频信号电路板,请问您选择什么材质的PCB板较好?

72、[问] 我是PCB设计的初学者,我想了解下去耦电容的选型规则是什么?还有值的大小怎么计算?

73、[问] 一个5khz的脉冲信号在板子上走20cm长,10mil宽的走线之后,其衰减能达到多少呢?

74、[问] 在高频中走的微带线走线与地平面的距离有什么要求吗?比如说大于1mm。还是没有太大的要求,只要差不多就可以了?还是要按共面波导计算?

75、[问] 如何布线才能尽可能地降低线间高频信号的串扰?

76、[问] 想请问在DC-DCConvertIC,在IC下方需要连接到地平面,透过Via连接到地平面,Via孔的数量多与少影响程度为何?

77、[问] 阻抗匹配时,若引脚给出的阻抗值为复数,即既有阻抗部分又有电抗部分,这时阻抗匹配如何做?光考虑电阻部分吗?

78、[问] 高频中集中参数和分布参数那种比较好?要怎么选择这两种方法比较合适呢?

79、[问] 双层板连接上下覆铜地的过孔分布有何要求?

80、[问] 如何在中频应用中,如何平衡放大器输入端的寄生电感和寄生电容?

81、[问] 怎样能有效减少电路元件间的干扰影响,以及放大器如何布局才能限度的抑制纹波的引入?

[答] 减少干扰的原则是:

- 减少辐射端;

- 加强被干扰的隔离、屏蔽和退偶;

- 减少开关电源的纹波输出;

- 足够的退偶滤波;

82、[问] 6层设计时,层的分配技巧,那些走线要走中间层?

83、[问] 在模拟地和数字地相连时,采用的方法是否在数字地处接一个合适的磁珠到模拟地?那这个磁珠要怎么选呢?

84、[问] 請问对于高于5G以上的讯号布局有何要注意的地方?

85、 [问] 电路中有高速逻辑器件时,布线长度为多大?

[答] 布线不怕长,就怕不对称或者有比较大的差,这样容易因为时延造成错误的逻辑。

86、[问] 在高速数字电路板中,有多个不同电压值的电源,铺电源平面时应该尽量采用多层电源平面还是在同一层电源平面上分开布置好?

87、[问] 在走差分线的时候由于空间限制,不能完全等距等长,请问是等距优先还是等长优先?

88、[问] 在PCB布局中,如何减少电磁干扰?另外哪些模块应该距离主控制芯片近一点?

89、[问] 考虑信号完整性时,如果只知道数字芯片的频率是1GHZ,一般会估算他的上升时间是为周期的1/10,即0.1ns。有何依据吗?

90、[问] 你好,请问ARM芯片提高电源的抗干扰,除了在电源输入端接入TVS管之外,电源输入端的输入脚要接电感比较好,还是磁珠比较好?

91、[问] pcb板在线能不能仿真一下,也就是怎么验证下板子有没有问题?

92、[问] 在pcb布线时有些人在信号的输入输出端串一个电阻进行端接,这个作用大吗?要如何选择这个电阻呢?那些地方需要这样做呢?

93、[问] 对影响电源的高速脉冲串有什么好的抑制方案或者成比较系统的处理方法吗?

94、[问] 高速PCB对板材有什么特殊要求没有?

95、[问] 关于信号线的阻抗匹配,请作点介绍和作法?

96、[问] 高频信号线的抗干扰措施有哪些?布线时应注意哪些方面?

97、[问] 为什么高速信号不用分数字和模拟地?

98、[问] 关于差分线的等长补偿,您为何就直接建议在驱动器端补偿呢?能解释一下吗?EricBogatin的书中也只是给出结论,但无解释。

99、[问] 在高频选用制板材料时,介电常数是不是越小越好呢?

100、[问] 多大频率的晶振要考虑MCU与晶振间的走线方式?

101、[问] 开关电源过来的直流电上面带有100mv左右的噪声,应该如何有效地滤除?

102、[问] 模拟电源是否也可以铺平面,是否和地的作用相同?

103、[问] 请问,两层电路板的覆铜,什么时候选择两面均覆,什么时候仅选择一面覆铜呢?

104、[问] 请问在高频(1GHz以上)板的设计中,过孔的大小及过孔间距有什么要求?阻抗匹配时需要考虑到的因素有哪些?板材需要注意么?差分走线与地平面的距离有什么注意事项?

[答] 如何需要综合考虑以上指标,建议做整体的电路仿真和调试,寄生效应会影响仿真效果,需要进行反复验证和尝试。

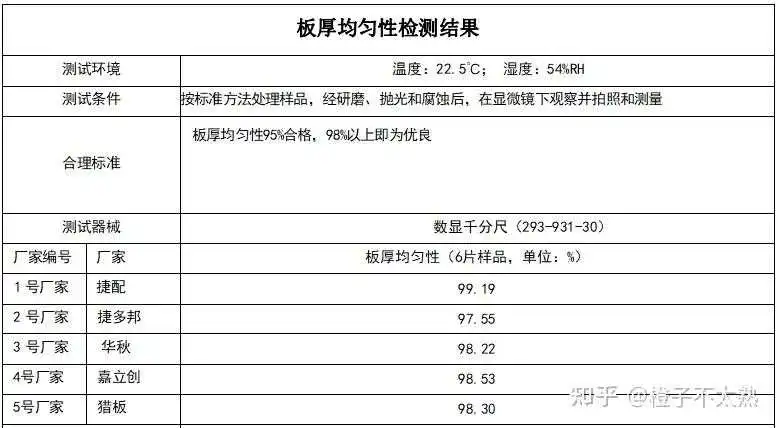

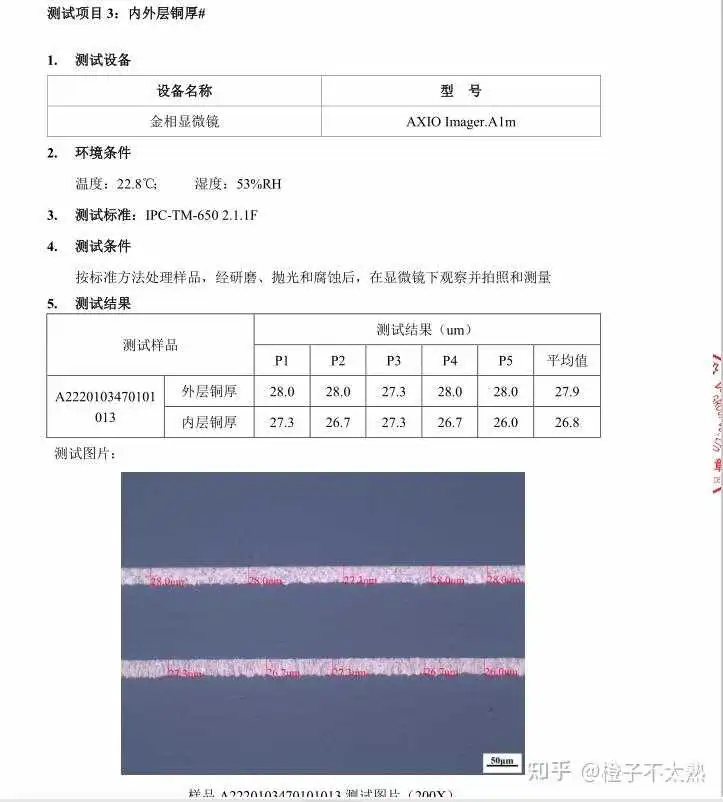

兜兜转转,时隔半月终于有时间写这个测评报告了。早些时候寄给检测机构检测的PCB产品,报告终于出来了。除了支付给检测机构的18888元,自己从各板厂打六层板的费用也有2000多,总经费2万+。六层板按照统一标准,工艺按照默认下单。

| 捷配 | 793元 |

| 嘉立创 | 907元 |

| 华秋 | 818元 |

| 猎板 | 921元 |

| 捷多邦 | 1034元 |

首先,我们这次检测结果的样品来自捷配、嘉立创、华秋、捷多邦、猎板五家。检测项目按照一般性PCB检测项目开始做。检测机构为华测,具备CNAS检测资质。

检测产品为五家的六层板,事先声明,表格为自行整理的对比图表,以方便比较。

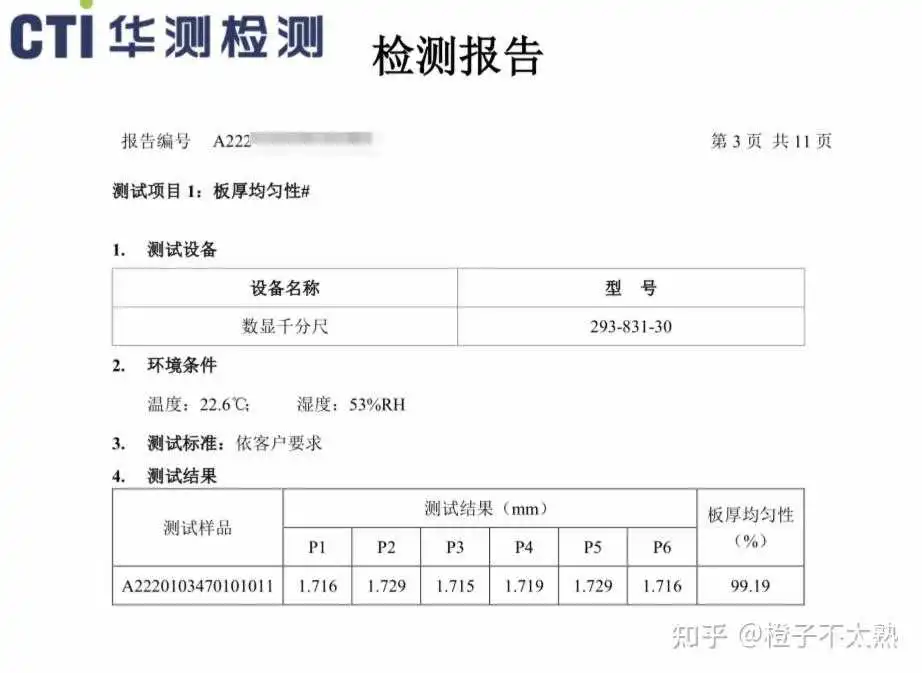

板厚均匀性检测,温度22.5摄氏度,适度54%RH。实验方法如上图

可以看到五家的板厚均匀性在97—99之间,最优的为捷配的六层板。关于板厚均匀性,可以解释为PCB板各层板厚的分布是否均匀,结果值为95%以上为合格,98%以上为优良。结果给出来,五家的六层板都是合格的。

检测机构报告展示:

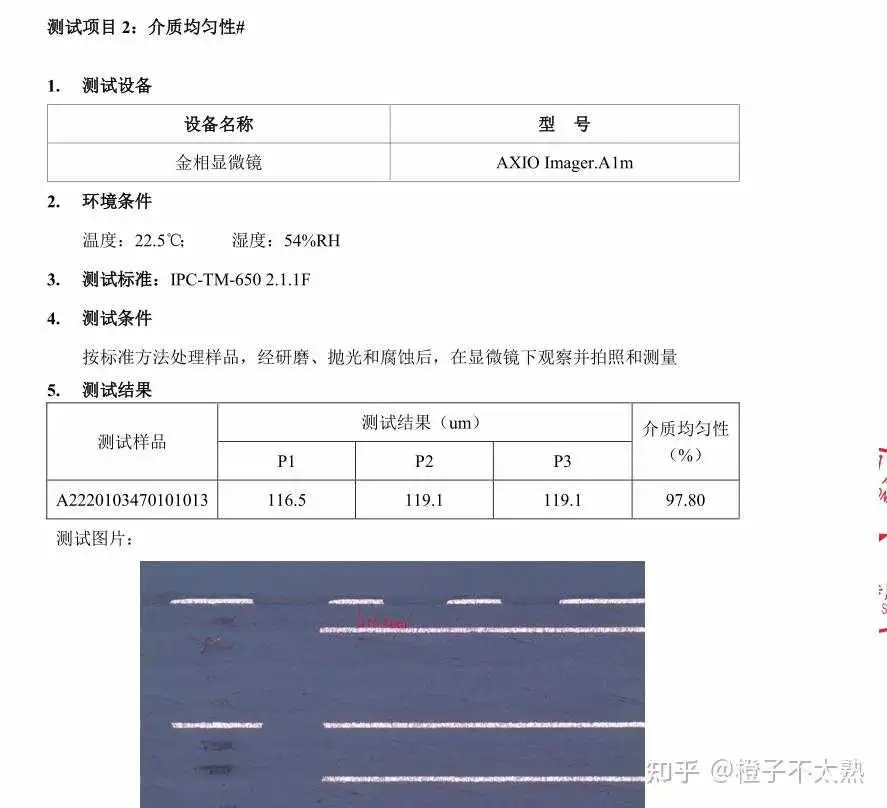

再看介质均匀性分析,介质是PCB导电的重要组成,一般规定介质层厚度均匀性厚度95%为合格,98%为优良。实测下来除了捷多邦的介质均匀性低于合格线,其他都是在合格线之上,捷配为优良。

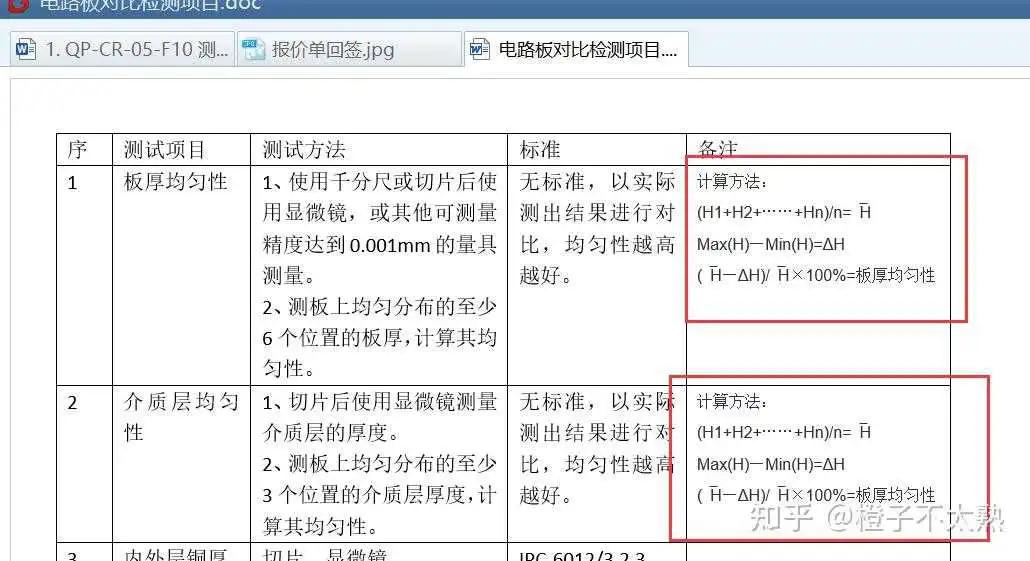

两个均匀性项目的分析得出的计量方法其实就是取每层厚度进行平均取值得出。为了增加取值的科学性,检测以此获取6个数据,6个数据相加除以n,得出H。以此增加检测严谨性。

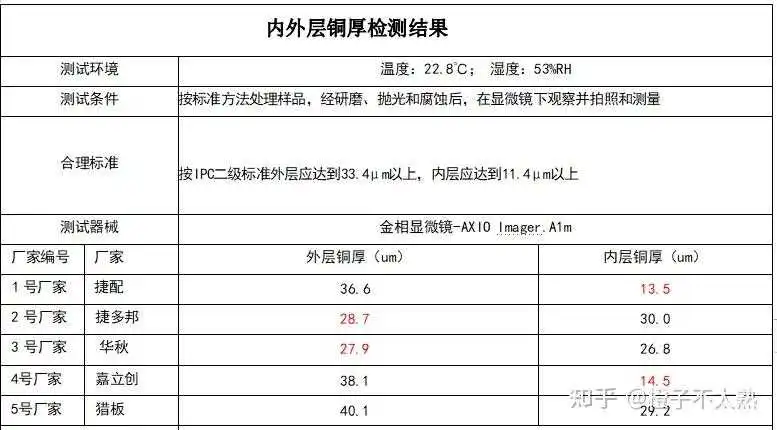

这点检测结果比较奇怪,可以发现五家厂家的内外层铜厚都有很大区别。

可能原因

1、下单时对铜厚参数要求没有一致

2、下单参数一致,单工厂没有按参数生产

可是翻查自己的下单记录,都是按照外层1OZ,内层0.5OZ的要求下单的。若按成品外层铜厚1OZ(μm),内层铜厚1/2OZ(17μm),按IPC二级标准,外层应达到33.4μm以上,内层应达到11.4μm以上。

按照这样的标准,标红的计价都是不符合要求的,捷配嘉立创内层铜厚比较薄,捷多邦华秋的外层铜厚较薄,表明铜厚合格率较低。

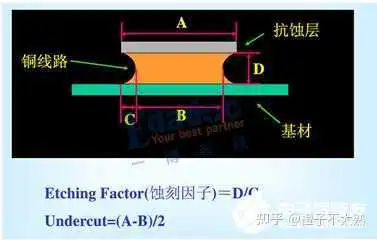

蚀刻是使用化学反应而移除多余材料的技术。PCB线路板生产加工对蚀刻质量的基本要求就是能够将除抗蚀层下面以外的所有铜层完全去除干净。

蚀刻液在蚀刻过程中,不仅向下而且对左右各方向都产生蚀刻作用侧蚀是不可避免的。侧蚀宽度与蚀刻深度之比称为蚀刻因子。我们的成品线路实际上是一倒立的梯形,蚀刻因子越大,具体参考为大于2-4,值越大越好,阻抗控制得也越好。通常我们的蚀刻精度公差是10mil及以下的线宽按照+/-1MIL控制,10mil以上的线宽公差按+/-10%管控。线宽越小,蚀刻的精度公差越难控制。

那我们看一下检测结果,在五家蚀刻因子方面,五家都是合格的,但是捷多邦较低,猎板是最高的,捷配也是在优良的水平线。

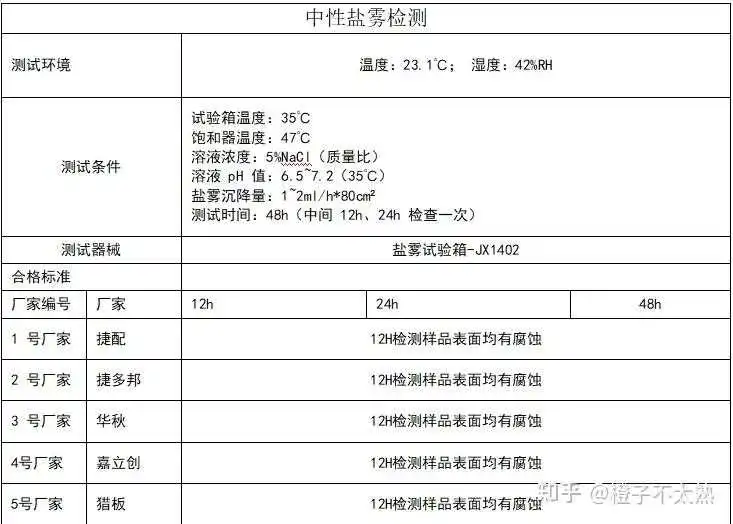

耐电压检测是在1000V的环境下进行检测,在60s时间内升压,都未发生火花和击穿现象,符合一般性要求。

盐雾试验是观察线路保护层(阻焊)层的耐受能力,这里五家的测试结果都是有腐蚀,原因是焊盘是锡和铜,都不是耐腐蚀的金属。这项检测出现了一点小小的误差,测试结果没有达到原来的预期。还有一项是离子污染度测试,由于自己的失误让对方理解错了,自己的锅。

以上是我通过专业检测机构(CNAS资质)获取的六层板检测结果,总的来说五家产品的样品存在一定的扎伊,但符合一般性需求,各项指标的区别已经表明可执行作为参考。当然,肉眼看得到的,比如丝印,焊盘等问题并没有在这次检测测试中,由于是抽样检测,并不代表各厂家整体的水平。

好久没有用AD了,感觉自己都手生了,一直想写一篇关于布局布线的,但自己总是总结不出来想要的东西(看来是自己的能力太低了),最近在凡亿PCB的公众号中看见了有一个PCB布局布线技巧100问,个人觉得是比较全面了,所以我没事的时候就把他总结了一下(这算是表明出处了吧)。

- 1、在PCB布局布线之前需要对整个板卡中元器件的布局进行设置。布局的时候主要是靠自己的想象(个人觉得这体现了一个人对原理图的理解和其画板的能力)。当然这其中也是有一定的规律的,我这里给大家说点自己的经验吧。在布局之前要先确定板子的形状和大小,这关乎制作的成本和现实中的实际使用。画好板子形状之后,主控芯片放在板卡的中心位置,当然这不是必须的,根据原理图和实际使用的情况在制定。外接顶针要放置在板卡的边缘位置。电源放置在板卡的开阔地带,便于散热。实时存储芯片放置在主芯片的周围便于存储。(这是我的一些个人经验当然只是一部分,有错误和想补充的可以在评论。

- 2、在板子上布置去耦电容,需要在合适的位置布置合适的电容。例:在模拟器件的供电端口就近添加,并且需要用不同的电容值去滤除不同频率的杂散信号。

- 3、叠层设计,对于制作时具体使用2层板,4层板,6层板还是…。这是没有具体要求的,采用多层板首先可以提供完整的地平面,另外可以提供更多的信号层,方便走线。所以叠层的时候根据自己的实际情况决定就行。

- 4、多层板布局时,因为电源和地层在内层,要注意不要有悬浮的地平面或电源平面,另外要确保打到地上的过孔确实连到了地平面上,最后是要为一些重要的信号加一些测试点,方便调试的时候进行测量。

- 5、在布线的时候可以模块化布线。将所有元器件分成几组分别进行布线。当然在布线之前需要对信号线做阻抗仿真计算出线宽和线和地的距离。电源线需要根据电流的大小决定线宽地在混合信号PCB时候一般不用“线”了,而是用整个平面,这样才能保证回路电阻最小,并且信号线下面有一个完整的平面。

- 6、线宽和与之匹配的过孔大小比例关系很难说有一个简单的比例关系,因为这两个的模拟不一样。一个是面传输一个是环状传输。对这种比例关系可以在网上找一个过孔的阻抗计算软件,然后保持过孔的阻抗和传输线的阻抗一致就行。

- 7、如果板卡中有多个AD转换芯片,要尽量将几个ADC放在一起模拟地数字地在ADC下方单点连接。

- 8、一个好的 PCB 设计,需要做到自身尽量少的向外发射电磁辐射,还要防止外来的电磁辐射对自身的干扰。最好的方法是屏蔽,阻止外部干扰进入。电路上,比如有 INA 时,需要在 INA 前加

RFI滤波器滤除 RF 干扰。 - 9、对于电路板的铺铜设置,如果内部有完整的地平面和电源平面,则顶层和底层可以不敷铜。

- 10、有些器件的引脚较细,有些人会担心 PCB 板上走线较粗,连接后会不会造成阻抗不匹配的问题?这要看是什么器件.而且器件的阻抗一般在数据手册上给出,一般和引脚粗细关系不大

- 11、差分线可以通过走蛇形线来解决等长的问题,现在大多数的 PCB 软件都可以自动走等长线,很方便

- 12、在设计 PCB 时,好的 EMI/EMC 设计必须一开始布局时就要考虑到器件的位置, PCB 叠层的安排,重要联机的走法, 器件的选择等。例如时钟产生器的位置尽量不要靠近对外的连接器,高速信号尽量走内层并注意特性阻抗匹配与参考层的连续以减少反射,器件所推的信号之斜率(slew rate)尽量小以减低高频成分,选择去耦合(decoupling/bypass)电容时注意其频率响应是否符合需求以降低电源层噪声。另外,注意高频信号电流之回流路径使其回路面积尽量小(也就是回路阻抗 loop impedance尽量小)以减少辐射, 还可以用分割地层的方式以控制高频噪声的范围,最后,适当的选择PCB 与外壳的接地点(chassis ground)。

- 13、蛇形走线,因为应用场合不同而具不同的作用:

- 如果蛇形走线在计算机板中出现,其主要起到一个滤波电感和阻抗匹配的作用,提高电路的抗干扰能力。计算机主机板中的蛇形走线,主要用在一些时钟信号中,如PCI-Clk,AGPCIK,IDE,DIMM 等信号线。

- 若在一般普通 PCB板中,除了具有滤波电感的作用外,还可作为收音机天线的电感线圈等等。如 2.4G 的对讲机中就用作电感。

- 对一些信号布线长度要求必须严格等长,高速数字 PCB 板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据)。如INTELHUB 架构中的 HUBLink,一共 13 根,使用 233MHz 的频率,要求必须严格等长,以消除时滞造成的隐患,绕线是惟一的解决办法。一般要求延迟差不超过 1/4 时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽、线长、铜厚、板层结构有关,但线过长会增大分布电容和分布电感,使信号质量有所下降。所以时钟 IC 引脚一般都接;" 端接,但蛇形走线并非起电感的作用。相反地,电感会使信号中的上升沿中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距最少是线宽的两倍。信号的上升时间越小,就越易受分布电容和分布电感的影响。

- 蛇形走线在某些特殊的电路中起到一个分布参数的 LC 滤波器的作用。

- 14、采用盲孔或埋孔是提高多层板密度、减少层数和板面尺寸的有效方法,并大大减少了镀覆通孔的数量。但相比较而言,通孔在工艺上好实现,成本较低,所以一般设计中都使用通孔。

- 15、高频信号布线时要注意:

- 信号线的阻抗匹配;

- 与其他信号线的空间隔离;

- 对于数字高频信号,差分线效果会更好;

- 16、在布板时,过孔的多少问题,对于低频信号,过孔不要紧,高频信号尽量减少过孔。如果线多可以考虑多层板;

- 17、如何避免布线时引入的噪声?数字地与模拟地要单点接地,否则数字地回流会流过模拟地对模拟电路造成干扰。

- 18、PCB 为了预防 PWM 等突变信号对模拟信号(如运放)产生的干扰,要从运放的几个接口入手,输入端要防止空间耦合干扰和 PCB 串扰(布局改善);电源需要不同容值去耦电容。测试可以用示波器的探头测试上面说的位置,判断出干扰从何而来。PWM 信号如果是通过低通滤波变成直流控制电压的话,可以考虑就进做滤波,或者并联对地一个小电容,让 PWM 的波形变圆,减少高频分量

- 19、对 PCB 走线的熔断电流如何考虑?参考0.15×线宽(mm)=A,这时最大电流。设计时候不能用熔断电流做预算。这样就是铜线的截面积。

总结一下,一个好的板子的标准是布局合理、功率线功率冗余度足够、高频阻抗匹配、低频走线简洁。

以上是我看过的一部分总结,个人能力有限。有不对的欠缺的欢迎大家一起讨论。

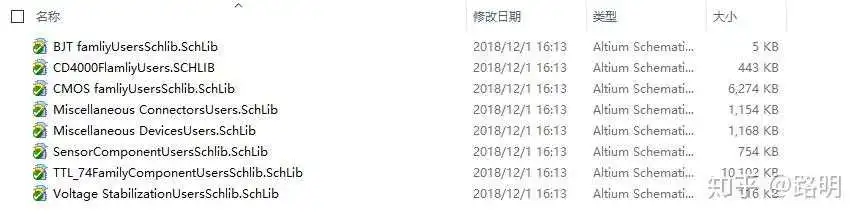

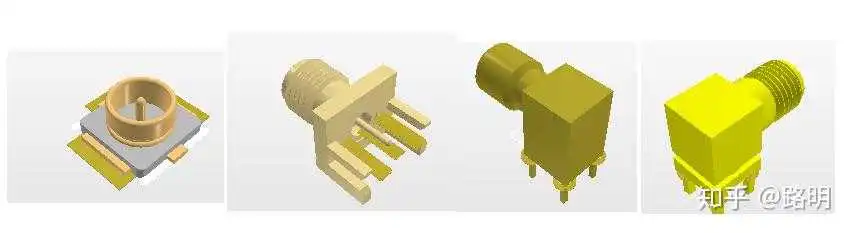

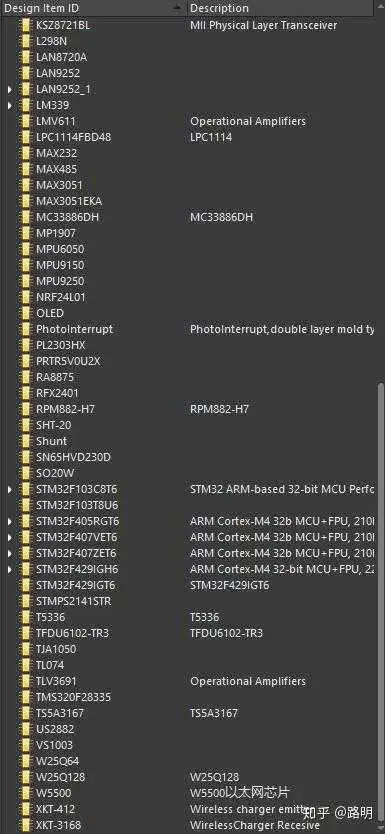

关注公众号,回复“AD库”

然后介绍文件夹

int 是继承。pcb是pcb库。sch是原理图库。

这是SCH库。

Miscellaneous DevicesUsers

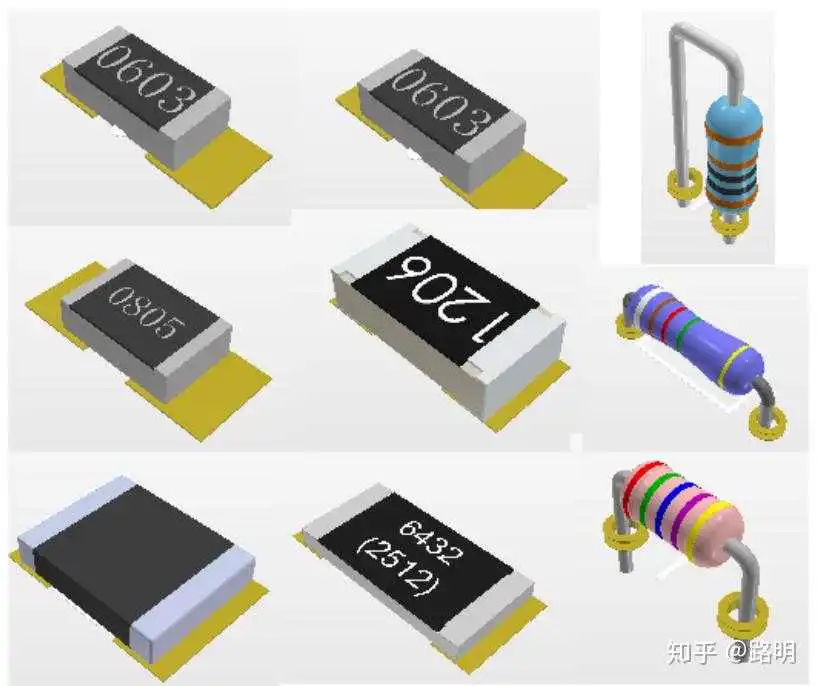

这个是最重要的库,包含了电阻、电容、电感、二极管、N管、NPN、常用开关等等。现在一一介绍。

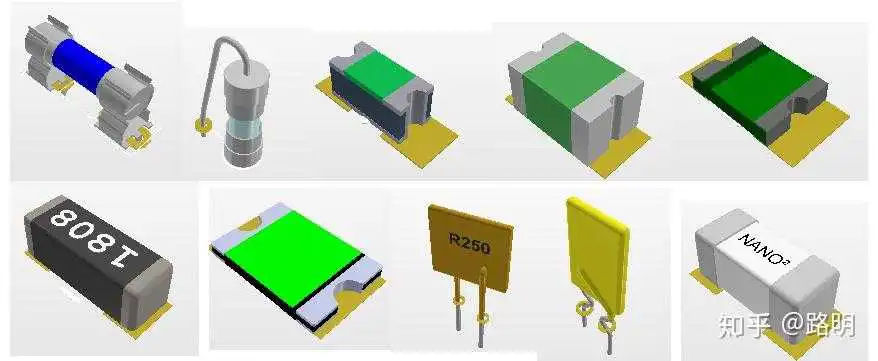

电阻-Res

电阻原理图比较简单,对应的PCB库比较麻烦,目前已经继承了很多

简陋的用PS拼接以下,大家凑合看。

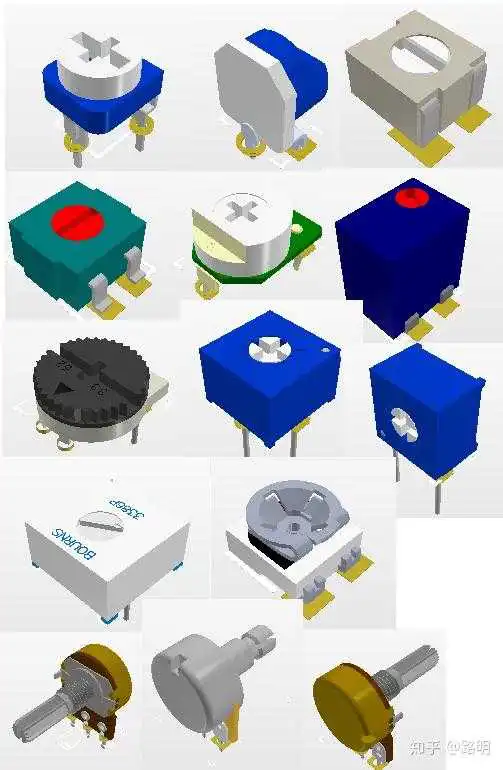

滑动电阻-Res Adj

排阻-Res Pack

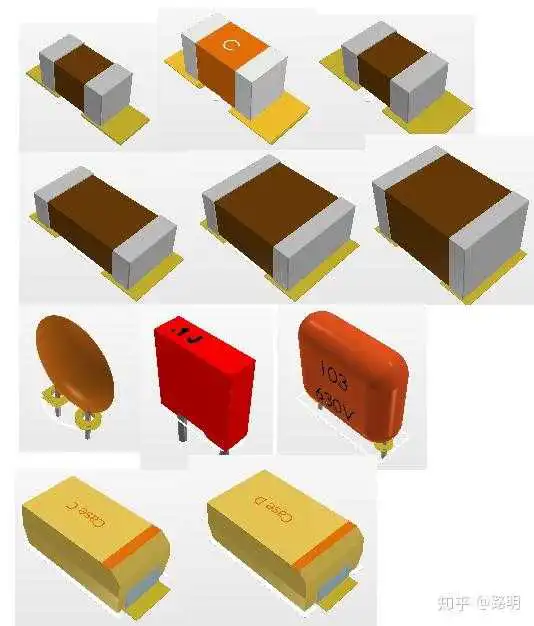

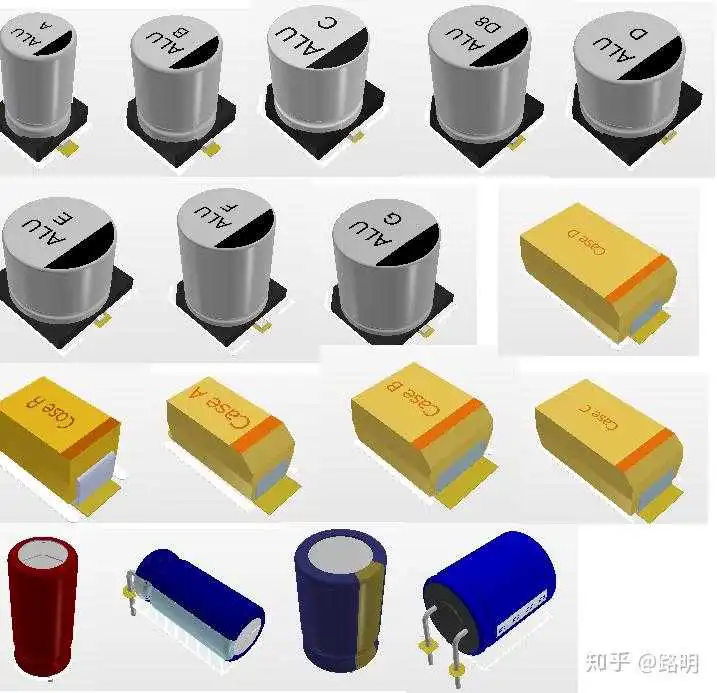

电容Cap

电解电容Cap Pol

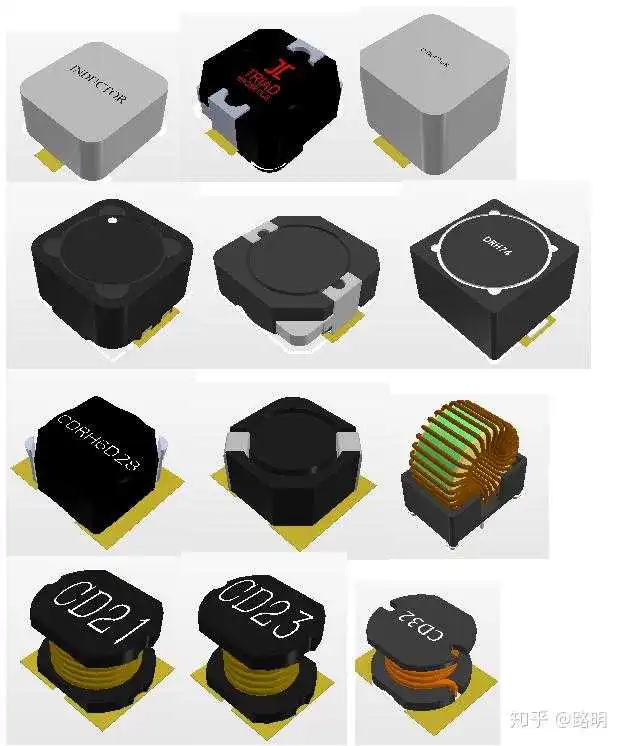

电感-Inductor

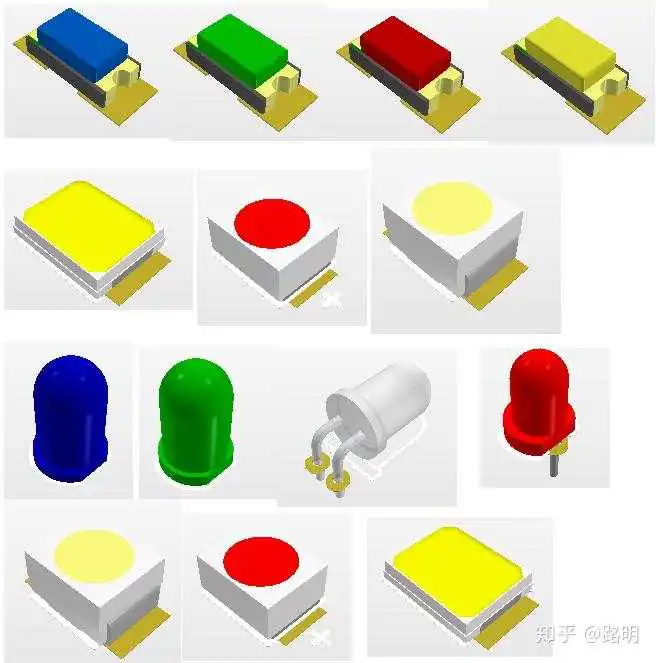

LED-led

晶振-XTAL

二极管-Diode

电池-Batter

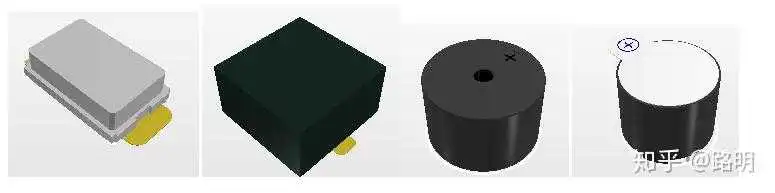

蜂鸣器-Beep

保险丝-Fuse

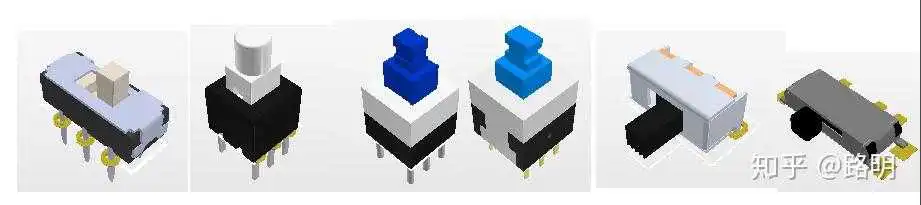

触点开关-SW-PB

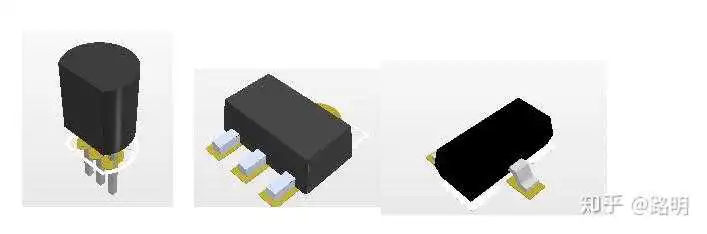

三极管-NPN PNP

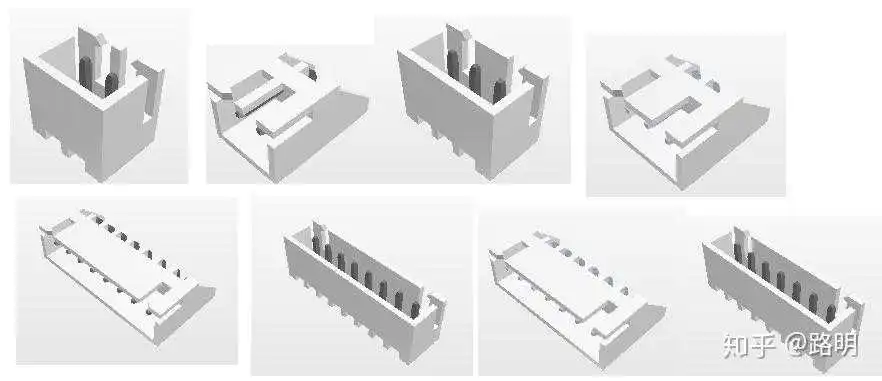

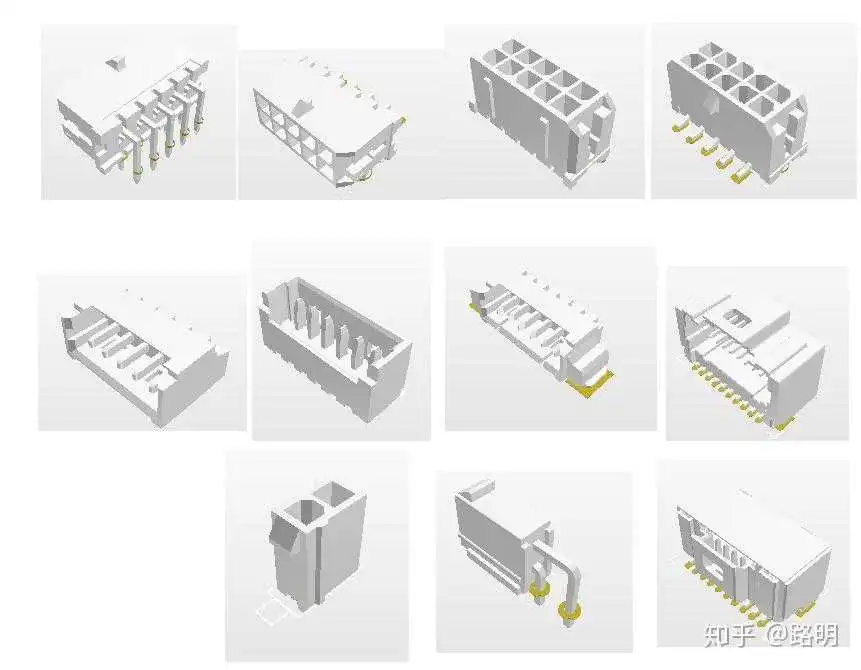

Miscellaneous ConnectorsUsers 为插针排母之类,这里面的东西更多,没有办法一一介绍。这里主要介绍几个系列

header

这是最基本的插针,里面主要有两个尺寸2.54mm、1.27mm、1mm两种。有

1mm和1.27mm和2.54排针排母,目前有以下几种。针数是从1-40针都有,当然,你想要更长的可以拼接一起。

2.54带卡口端子 XH-CON-2.54

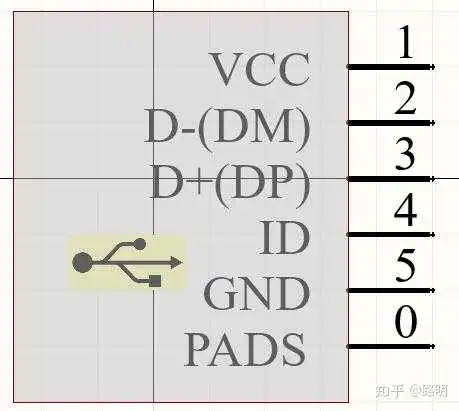

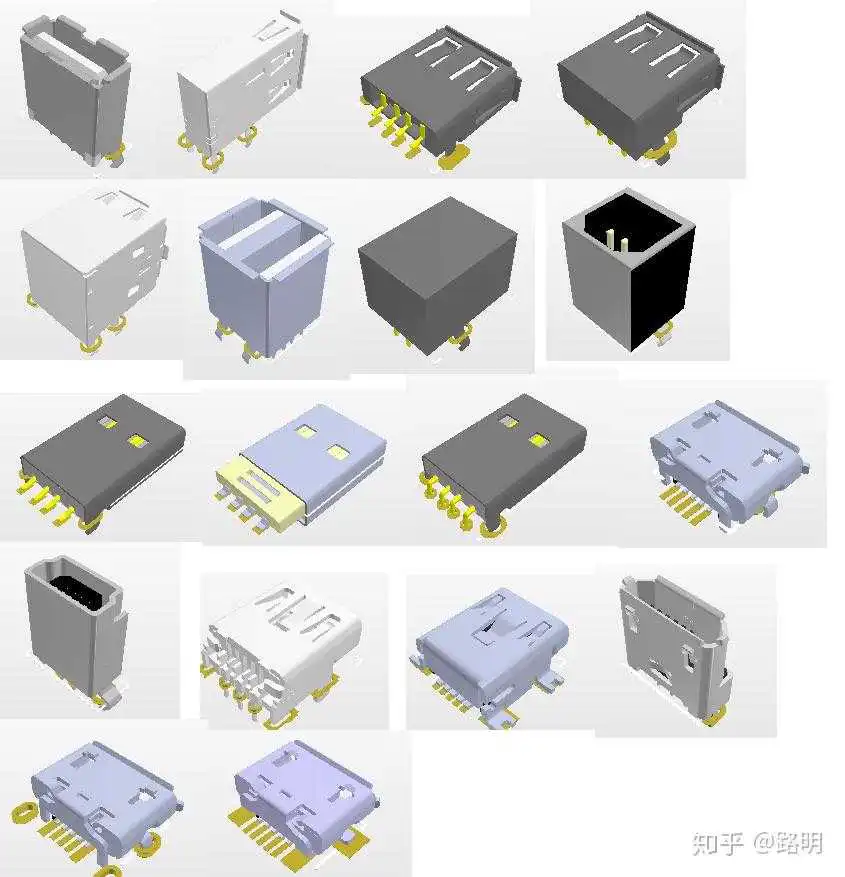

USB

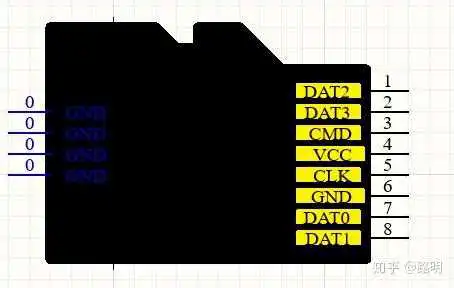

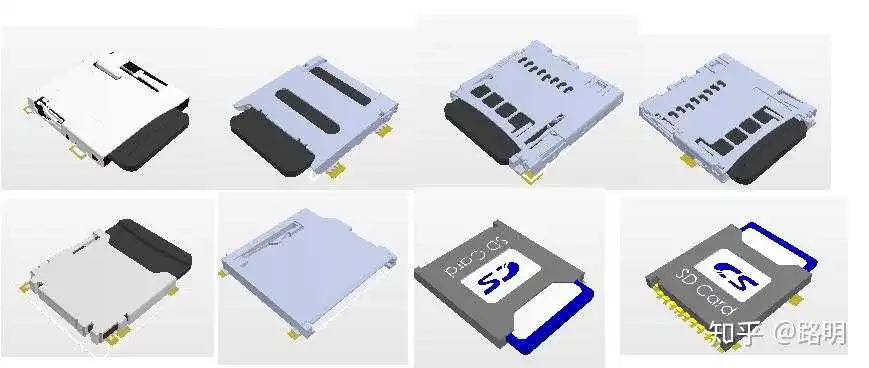

TF卡 TF

网口

无线插头

SIM

MOLEX插头

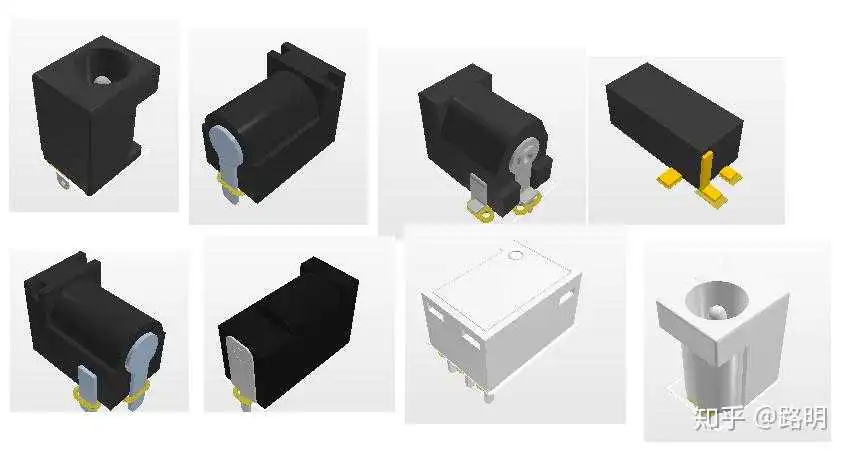

DP

电源插头

格式插头

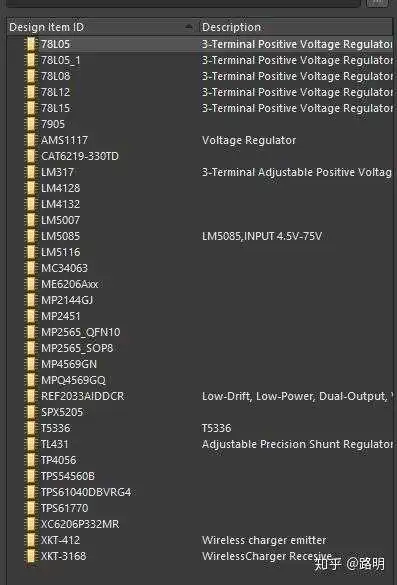

Voltage StabilizationUsersSchlib 主要包含了稳压原件。主要是德州仪器稳压原件。

SensorComponentUsersSchlib 是传感器元器件。一般比赛的肯定都是有的。如图

一些一般的封装主要在 ST-Microelectronics FootprintsUsers

这里有很多常规封装并增加了3D视图效果。大家可以自行查询

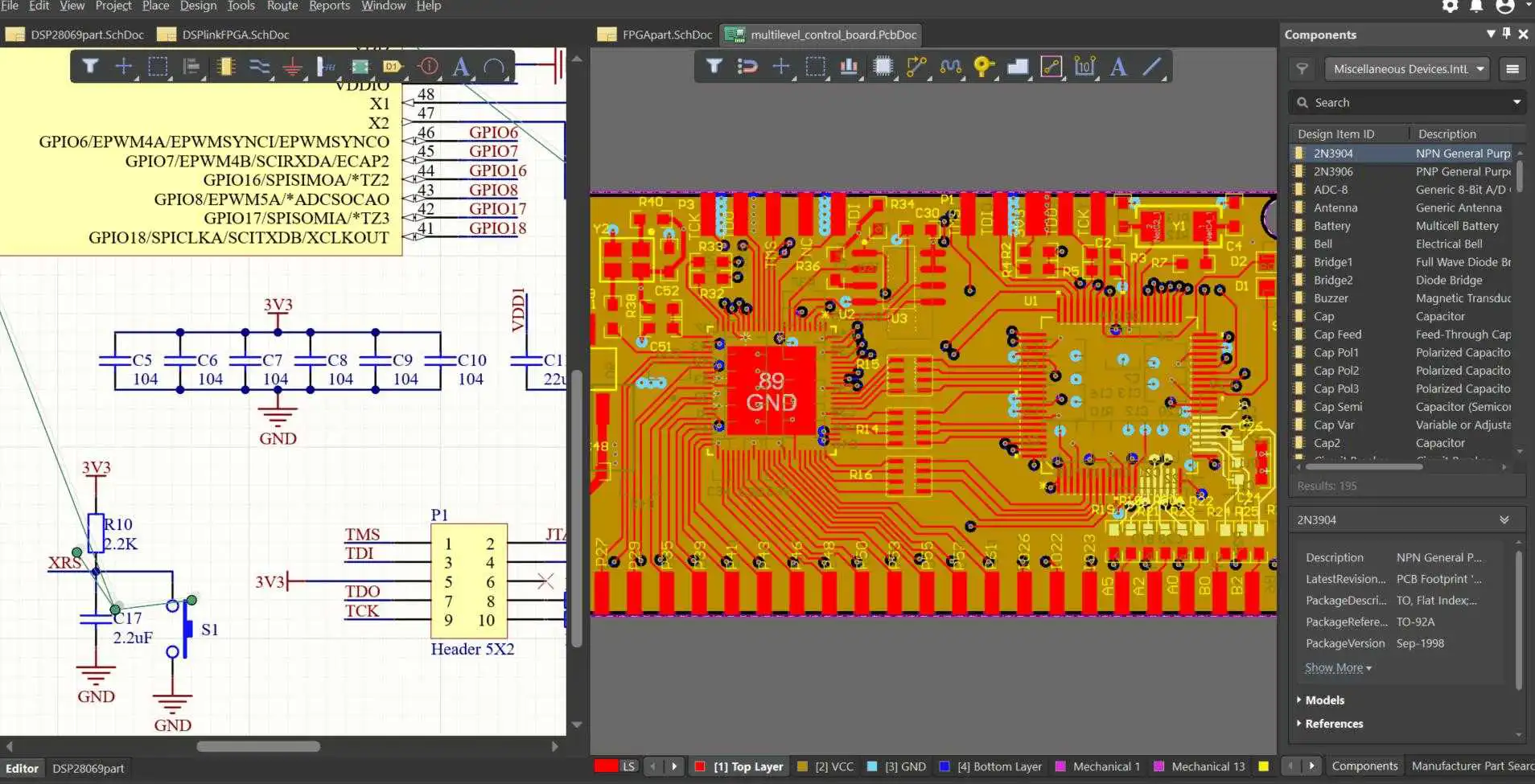

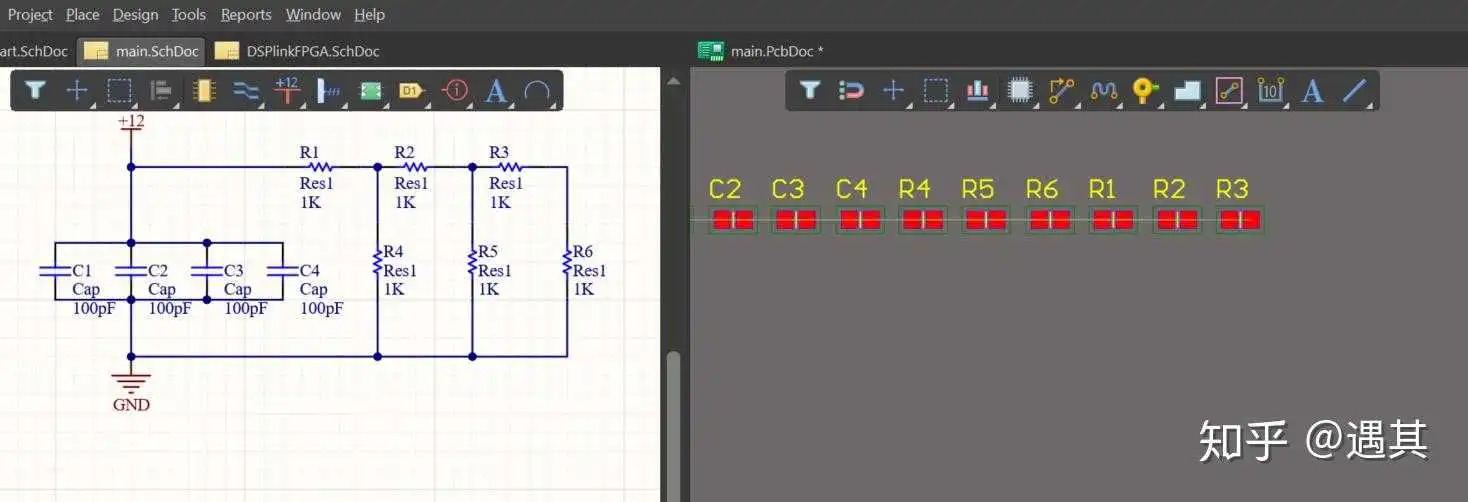

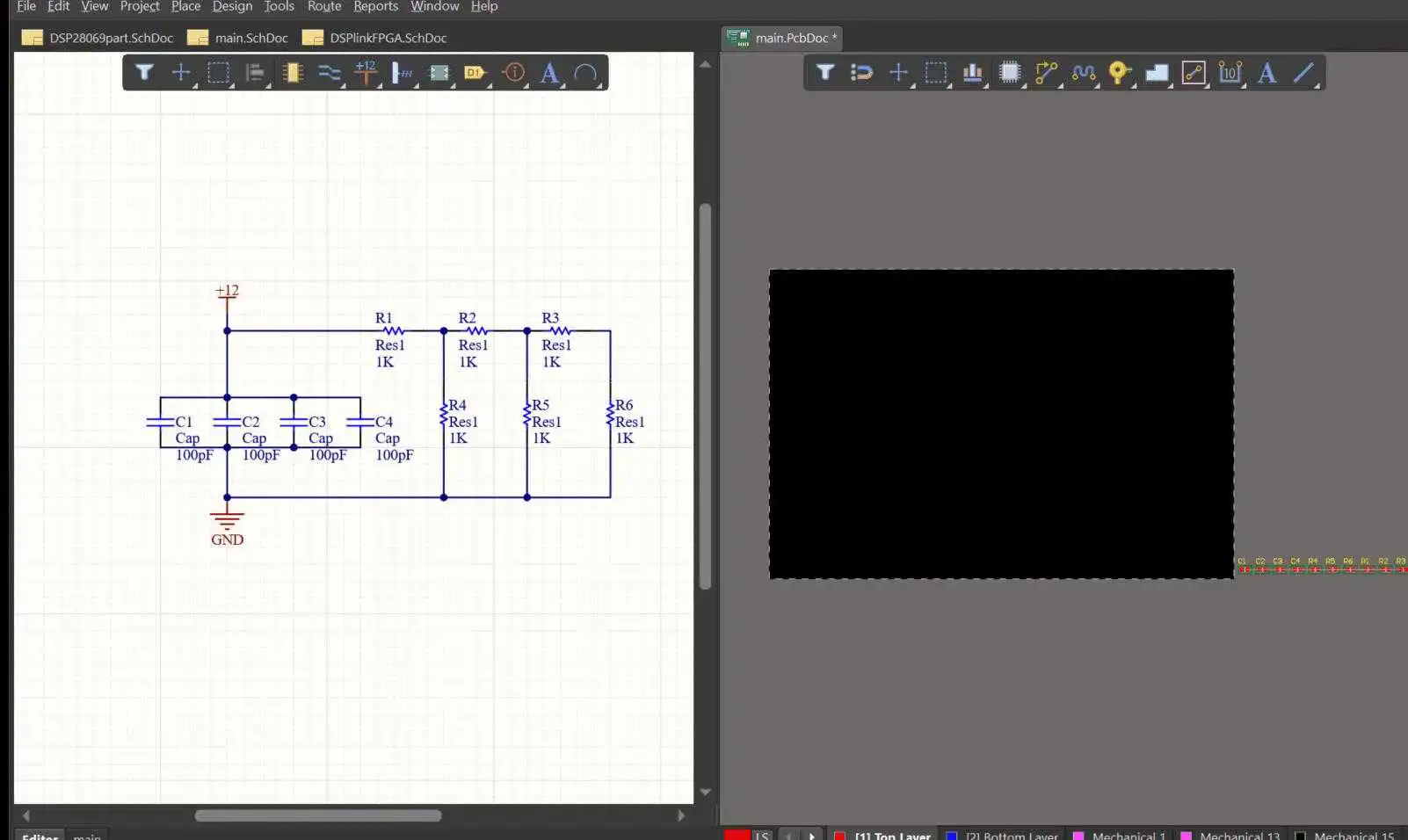

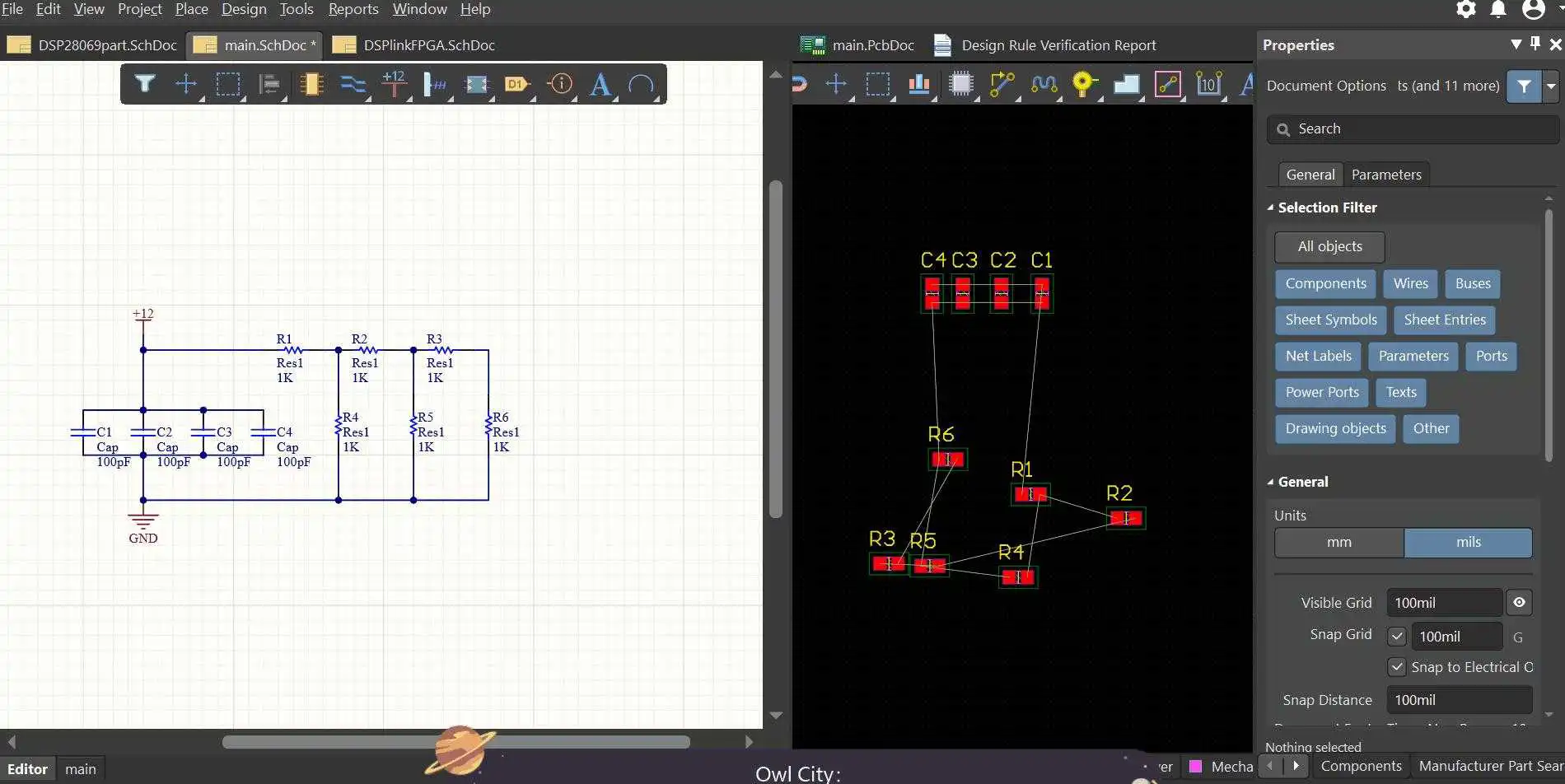

如果你的工作学习和硬件打交道,那么你肯定知道也用过Altium Designer。作为一个使用了很多年这个软件的萌新,我直到现在才知道原来以前软件的使用实在是太浅显了!也是因为自己只会一些简单的操作而使得使用软件的过程中浪费了很多的时间(虽然我发现身边的同学仿佛使用技巧掌握得和我也差不太多),然而只要再掌握一点点软件的使用技巧,一定能让画板子的时候快的飞起来,大佬请轻喷绕行,文章只适合比较经验不是很多的像我这样的萌新。废话不多说,进入正题。

这个问题其实可以用交叉探针(Cross Probe)解决,这是网上都能查到的办法。然而这个方法让我使用特别蛋疼。

首先,探针探到的元件会在PCB中放得特别大,导致整个页面只能看到这个元件了,找到之后还得缩小视图,非常影响体验。如图

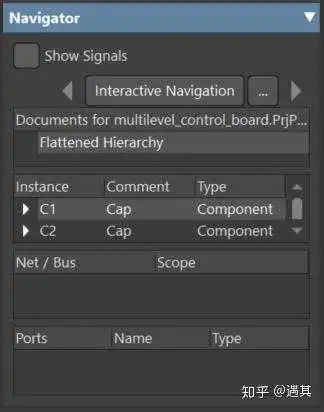

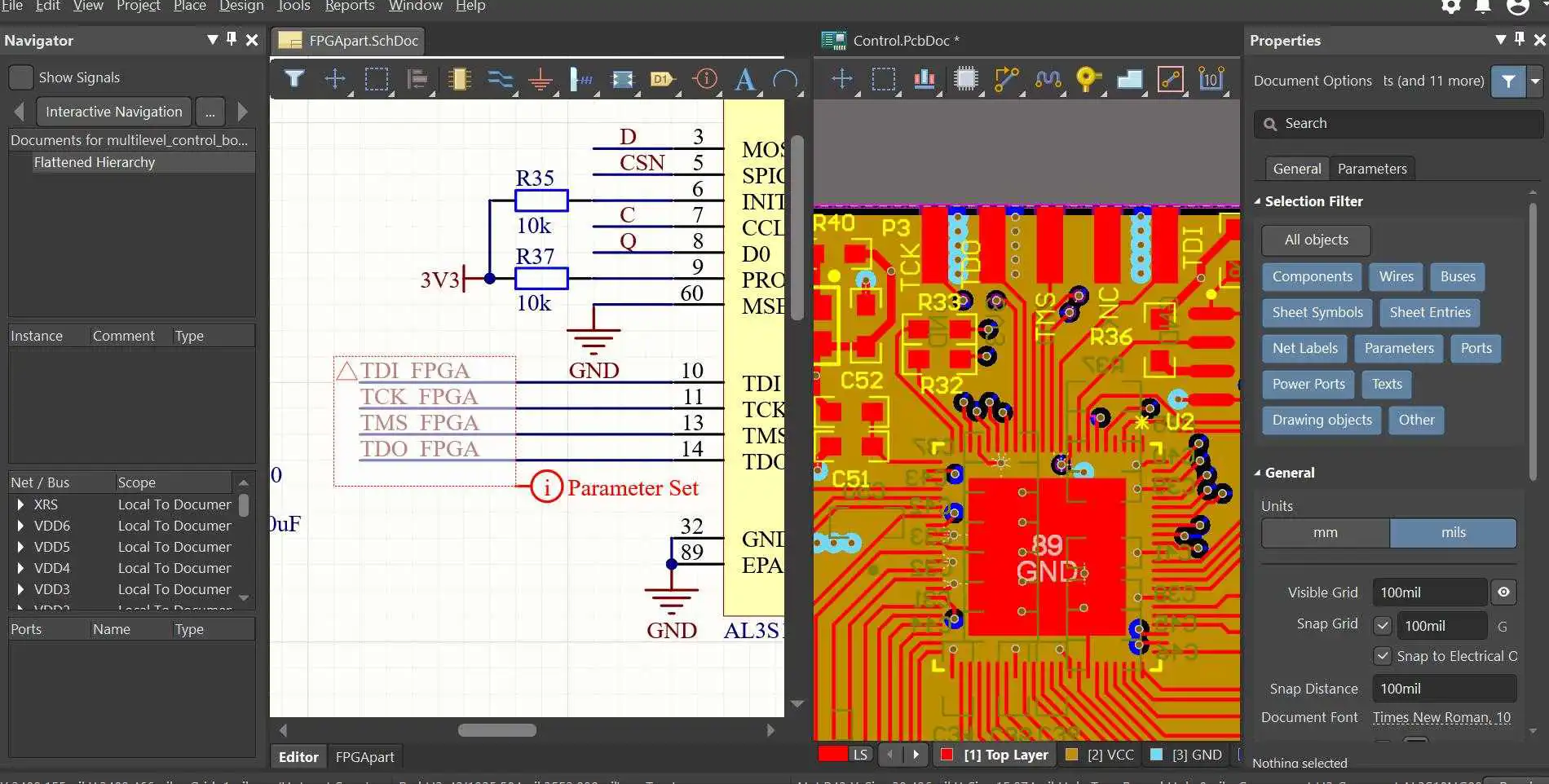

我苦苦寻找了很久如何在使用交叉探针的时候不放大元件,终于找到了设置的地方。打开屏幕右下角的Panel,选择Navigator,弹出窗口如图所示

在里面任意一个窗口,比如Instance窗口里面右键,取消勾选Zoom On Objects,问题解决。这样每次就不会放大到整个屏幕了,还可以按照需求选择交叉探针的勾选效果,有Dim(变暗),Zoom on objects(放大)还有selected(选择)。

不过这样其实每次还要按一下进入交叉探针模式才能用,还是有点麻烦。其实还有更简单的办法,直接打开Cross Select Mode即可,点击Tools->Cross Select Mode(快捷键Ctrl+Shift+X),这样直接在原理图里选中元件的时候,PCB里面同样也会同时选中。

即便是我们能够通过原理图来选中PCB中的元件,但是元件很多时候都是成百上千个,一个一个地点开再查找效率实在是太低了。这里我演示怎么一次性Layout下图中的所有电容,仅仅是示意,其他场合自行探索吧。

演示如下,先在原理图中框选要Layout的元件,这个时候在PCB界面应该可以看到元件被选中了,随后点到PCB的窗口界面(确保这个时候元件仍然处于被选中的状态),进入Tools,选择Component Placement,子菜单选择Reposition selected components。然后选中的元件就会一个一个蹦出来啦,不用去在一大堆元件中去找啦。

而这我还觉得不方便,毕竟去点Tools->Component Placement->Reposition Selected Components还是很麻烦(选项藏得很深),那么就可以用快捷键大法了,眼尖的你可能发现了我已经绑定了Ctrl+Shift+P这个快捷键,当然你也可以按照你个人的喜好设定快捷键(设定办法自行Google吧)

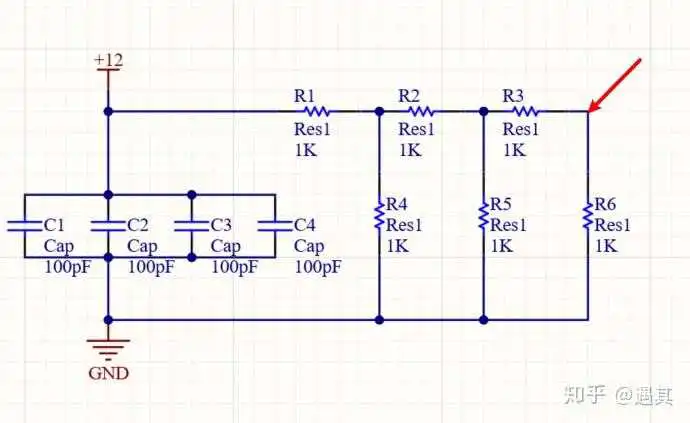

举个例子,在有电压比较高网络的PCB中,需要仔细考虑其Layout的时候的Clearance(甚至不同的层的Clearence需要的也会不同);或者说有的差分线需要一个镜像面的完整检查Rules。这种时候我们都需要对单独的某些网络设置不同的Rules。最容易想到的办法就是通过Custom Query去筛选我们想要单独设置的Rules,但是这样其实不太直观,而且也比较麻烦。这个时候使用Parameter Set工具再合适不过了。比如我们设置下图中箭头所指的网络的Clearance的间距为20mil。

操作如下

这样我们就设置了这个网络的Clearance规则。当然不仅仅是可以设置Clearance,其他的Rules可以自行探索。如果需要对一片区域内的网络都设置同样的规则,可以先放置一个Blanket框选需要设置的区域,再设置ParameterSet即可

可以。使用Net Class来解决这个问题。Class就是类的意思,所以Net Class顾名思义也就是把Net分为一个一个的类来进行单独管理。具体操作办法就是使用上面提到的ParameterSet来设置网络的Net Class,随后在PCB面板中进行单独查看。

暂时分享到这么多,如果这篇文章有帮助到你的话,请不要吝惜你的点赞哦!

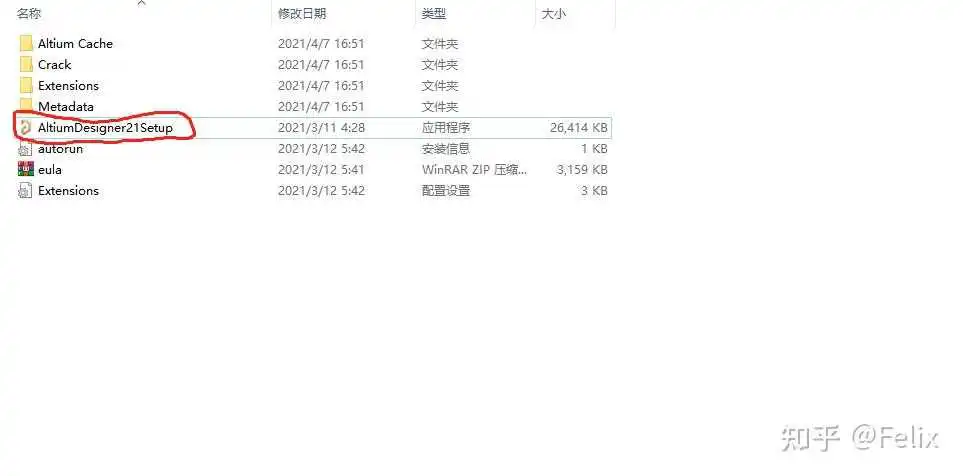

1、提取安装文件

链接:https://pan.baidu.com/s/15bZ8fPP5xnn0kuHxLeW30Q

提取码:fq4o

2、解压后双击AltiumDesigner21Setup.exe进行安装

3、将上图中crack文件夹里的shfolder.dll文件复制到C:\Program Files\Altium\AD21\安装目录中;

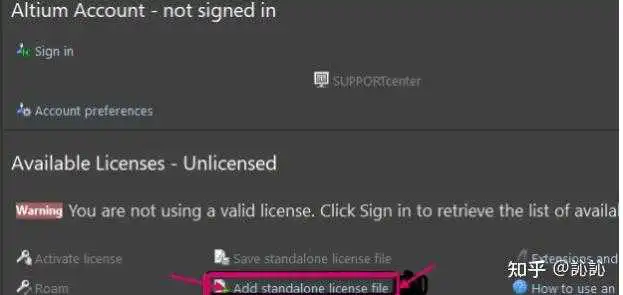

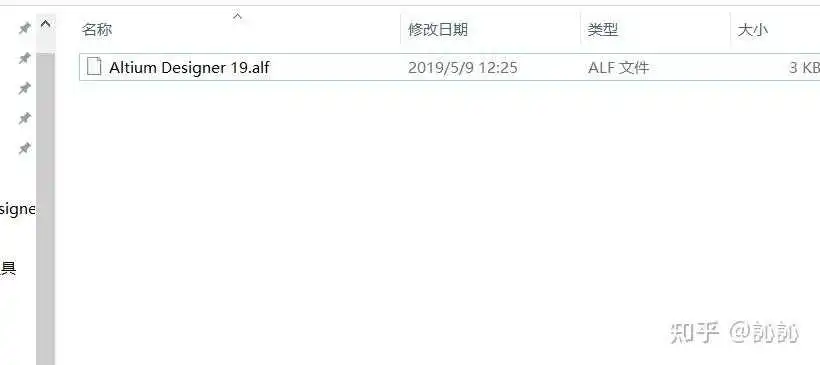

4、打开AD21,进入license management界面,点击add standalone license file,进入Crack->licenses选择一个license文件。

5、激活成功教程完毕

AD18层次原理图绘制_a的博客-CSDN博客_ad层次原理图

PCB多层板的层:

a.信号层(Signal Layers): 信号层包括Top Layer、 Bottom Layer 、Mid Layer 1……30。这些层都是具有电气 连接的层,也就是实际的铜层。中间层是指用于布线的中间板层,该层中布的是导线。

b.内层(Internal Plane): Internal Plane 1……16,这些层一般连接到地和电源上,成为电源层和地层,也具有电气连接作用,也是实际的铜层,但该层一般情况下不布线,是由整片铜膜构成。

c.丝印层(Silkscreen Overlay): 包括顶层丝印层(Top overlay) 和底层丝印层Bottom overlay) 。定义顶层和 底层的丝印字符,就是一般在阻焊层之上印的一些文字符号,比如元件名称、元件符号、元件管脚和版权等,方便以后的电路焊接和查错等。

d.锡膏层(Paste Mask): 包括顶层锡膏层(Top paste) 和底 层锡膏层(Bottom paste) ,指我们可以看到的露在外面 的表面贴装焊盘,也就是在焊接前需要涂焊膏的部分。所以,这一层在焊盘进行热风整平和制作焊接钢网时也有用。

f.机械层(Mechanical Layers): 最多可选择 16 层机械加工层。设计双面板只需要使用默认选项 Mechanical Layer 1。

g.禁布层(Keep Out Layer) : 定义布线层的边界。定 义了禁止布线层后,在以后的布线过程中,具有电气特性的布线不可以超出禁止布线层的边界。

h.钻孔层(Drill Layer): 包括钻孔引导层(Drill guide) 和钻 孔数据层(Drill drawing) ,是钻孔的数据。

f.多层(Multi-layer) :指PCB多层板板的所有层。

Altium Designer中各层的含义

mechanical, 机械层

keepoutlayer禁止布线层

topoverlay顶层丝印层

bottomoverlay底层丝印层

toppaste,顶层焊盘层

bottompaste底层焊盘层

topsolder顶层阻焊层

bottomsolder底层阻焊层

drillguide,过孔引导层

drilldrawing过孔钻孔层

1 Signal layer(信号层)

信号层主要用于布置电路板上的导线。Protel 99 SE提供了32个信号层,包括Top layer(顶层),Bottom layer(底层)和30个MidLayer(中间层)。

2 Internal plane layer(内部电源/接地层)

Protel 99 SE提供了16个内部电源层/接地层.该类型的层仅用于多层板,主要用于布置电源线和接地线.我们称双层板,四层板,六层板,一般指信号层和内部电源/接地层的数目。

3 Mechanical layer(机械层)

Protel 99 SE提供了16个机械层,它一般用于设置电路板的外形尺寸,数据标记,对齐标记,装配说明以及其它的机械信息。这些信息因设计公司或PCB多层板制造厂家的要求而有所不同。执行菜单命令Design|Mechanical Layer能为电路板设置更多的机械层。另外,机械层可以附加在其它层上一起输出显示。

4 Solder mask layer(阻焊层)

在焊盘以外的各部位涂覆一层涂料,如防焊漆,用于阻止这些部位上锡。阻焊层用于在设计过程中匹配焊盘,是自动产生的。Protel 99 SE提供了Top Solder(顶层)和Bottom Solder(底层)两个阻焊层。

5 Paste mask layer(锡膏防护层,SMD贴片层)

它和阻焊层的作用相似,不同的是在机器焊接时对应的表面粘贴式元件的焊盘。

Protel 99 SE提供了Top Paste(顶层)和Bottom Paste(底层)两个锡膏防护层。

主要针对PCB多层板板上的SMD元件。如果板全部放置的是Dip(通孔)元件,这一层就不用输出Gerber文件了。在将SMD元件贴PCB多层板板上以前,必须在每一个SMD焊盘上先涂上锡膏,在涂锡用的钢网就一定需要这个Paste Mask文件,菲林胶片才可以加工出来。

Paste Mask层的Gerber输出最重要的一点要清楚,即这个层主要针对SMD元件,同时将这个层与上面介绍的Solder Mask作一比较,弄清两者的不同作用,因为从菲林胶片图中看这两个胶片图很相似。

6 Keep out layer(禁止布线层)

用于定义在电路板上能够有效放置元件和布线的区域。在该层绘制一个封闭区域作为布线有效区,在该区域外是不能自动布局和布线的。

7 Silkscreen layer(丝印层)

丝印层主要用于放置印制信息,如元件的轮廓和标注,各种注释字符等。Protel 99 SE提供了Top Overlay和Bottom Overlay两个丝印层。一般,各种标注字符都在顶层丝印层,底层丝印层可关闭。

8 Multi layer(多层)

电路板上焊盘和穿透式过孔要穿透整个电路板,与不同的导电图形层建立电气连接关系,因此系统专门设置了一个抽象的层—多层。一般,焊盘与过孔都要设置在多层上,如果关闭此层,焊盘与过孔就无法显示出来。

阻焊层和助焊层的区分

阻焊层:solder mask,是指板子上要上绿油的部分;因为它是负片输出,所以实际上有solder mask的部分实际效果并不上绿油,而是镀锡,呈银白色!

助焊层:paste mask,是机器贴片时要用的,是对应所有贴片元件的焊盘的,大小与toplayer/bottomlayer层一样,是用来开钢网漏锡用的。

要点:两个层都是上锡焊接用的,并不是指一个上锡,一个上绿油;那么有没有一个层是指上绿油的层,只要某个区域上有该层,就表示这区域是上绝缘绿油的呢?暂时我还没遇见有这样一个层!我们画的PCB多层板板,上面的焊盘默认情况下都有solder层,所以制作成的PCB多层板板上焊盘部分是上了银白色的焊锡的,没有上绿油这不奇怪;但是我们画的PCB多层板板上走线部分,仅仅只有toplayer或者bottomlayer层,并没有solder层,但制成的PCB多层板板上走线部分都上了一层绿油。

那可以这样理解:

1、阻焊层的意思是在整片阻焊的绿油上开窗,目的是允许焊接!

2、默认情况下,没有阻焊层的区域都要上绿油!

3、paste mask层用于贴片封装!SMT封装用到了:toplayer层,topsolder层,toppaste层,且toplayer和toppaste一样大小,topsolder比它们大一圈。 DIP封装仅用到了:topsolder和multilayer层(经过一番分解,我发现multilayer层其实就是toplayer,bottomlayer,topsolder,bottomsolder层大小重叠),且topsolder/bottomsolder比toplayer/bottomlayer大一圈。

PCB多层板的各层定义及描述:

1、TOP LAYER(顶层布线层):设计为顶层铜箔走线。如为单面板则没有该层。

2、BOMTTOM LAYER(底层布线层):设计为底层铜箔走线。

3、TOP/BOTTOM SOLDER(顶层/底层阻焊绿油层):顶层/底层敷设阻焊绿油,以防止铜箔上锡,保持绝缘。在焊盘、过孔及本层非电气走线处阻焊绿油开窗。

焊盘在设计中默认会开窗(OVERRIDE:0.1016mm),即焊盘露铜箔,外扩0.1016mm,波峰焊时会上锡。建议不做设计变动,以保证可焊性;

过孔在设计中默认会开窗(OVERRIDE:0.1016mm),即过孔露铜箔,外扩0.1016mm,波峰焊时会上锡。如果设计为防止过孔上锡,不要露铜,必须将过孔的附加属性SOLDER MASK(阻焊开窗)中的PENTING选项打勾选中,则关闭过孔开窗。

另外本层也可单独进行非电气走线,则阻焊绿油相应开窗。如果是在铜箔走线上面,则用于增强走线过电流能力,焊接时加锡处理;如果是在非铜箔走线上面,一般设计用于做标识和特殊字符丝印,可省掉制作字符丝印层。 4、TOP/BOTTOM PASTE(顶层/底层锡膏层):该层一般用于贴片元件的SMT回流焊过程时上锡膏,和印制板厂家制板没有关系,导出GERBER时可删除,PCB多层板设计时保持默认即可。

5、TOP/BOTTOM OVERLAY(顶层/底层丝印层):设计为各种丝印标识,如元件位号、字符、商标等。

6、MECHANICAL LAYERS(机械层):设计为PCB多层板机械外形,默认LAYER1为外形层。其它LAYER2/3/4等可作为机械尺寸标注或者特殊用途,如某些板子需要制作导电碳油时可以使用LAYER2/3/4等,但是必须在同层标识清楚该层的用途。

7、KEEPOUT LAYER(禁止布线层):设计为禁止布线层,很多设计师也使用做PCB多层板机械外形,如果PCB多层板上同时有KEEPOUT和MECHANICAL LAYER1,则主要看这两层的外形完整度,一般以MECHANICAL LAYER1为准。建议设计时尽量使用MECHANICAL LAYER1作为外形层,如果使用KEEPOUT LAYER作为外形,则不要再使用MECHANICAL LAYER1,避免混淆!

8、MIDLAYERS(中间信号层):多用于多层板,我司设计很少使用。也可作为特殊用途层,但是必须在同层标识清楚该层的用途。

9、INTERNAL PLANES(内电层):用于多层板,我司设计没有使用。

10、MULTI LAYER(通孔层):通孔焊盘层。

11、DRILL GUIDE(钻孔定位层):焊盘及过孔的钻孔的中心定位坐标层。

12、DRILL DRAWING(钻孔描述层):焊盘及过孔的钻孔孔径尺寸描述层。

在DESIGN--OPTION里有:

(信号层)、Internal Planes

(内部电源/接地层)、Mechanical

Layers(机械层)、

Masks(阻焊层)、

Silk screen(丝印层)、

Others(其他工作层面)

及System(系统工作层),

在PCB多层板设计时执行菜单命令 [Design]设计/[Options...]选项 可以设置各工作 层的可见性。

一、Signal Layers(信号层)

Protel98、Protel99提供了16个信号层:Top (顶层)、Bottom(底层)和Mid1-Mid14(14个中间层)。

信号层就是用来完成印制电路板铜箔走线的布线层。在设计双面板时,一般只使用Top(顶层)和Bottom(底层)两层,

当印制电路板层数超过4层时,就需要使用Mid(中间布线层)。

二、Internal Planes(内部电源/接地层)

Protel98、Protel99提供了Plane1-Plane4(4个内部电源/接地层)。内部电源/接地层主要用于4层以上印制电路板作为电源和接地专用布线层,双面板不需要使用。

三、Mechanical Layers(机械层)

机械层一般用来绘制印制电路板的边框(边界),通常只需使用一个机械层。有Mech1-Mech4(4个机械层)。

四、Drkll Layers(钻孔位置层)

共有2层:“Drill Drawing”和“Drill Guide”。用于绘制钻孔孔径和孔的定位。

五、Solder Mask(阻焊层)

共有2层:Top(顶层)和Bottom(底层)。阻焊层上绘制的时印制电路板上的焊盘和过孔周围的保护区域。

六、Paste Mask(锡膏防护层)

共有2层:Top(顶层)和Bottom(底层)。锡膏防护层主要用于有表面贴元器件的印制电路板,这时表帖元器件的安装工艺所需要的,无表帖元器件时不需要使用该层。

七、Silkscreen(丝印层)

共有2层:Top(顶层)和Bottom(底层)。丝印层主要用于绘制文字说明和图形说明,如元器件的外形轮廓、标号和参数等。

八、Other(其它层)

共有8层:“Keep Out(禁止布线层)”、“Multi Layer(设置多层面)”、“Connect(连接层)”“DRC Error(错误层)”、2个“Visible Grid(可视网格层)”“Pad Holes(焊盘孔层)”和“Via Holes(过孔孔层)”。其中有些层是系统自己使用的如Visible Grid(可视网格层)就是为了设计者在绘图时便于定位。而Keep Put(禁止布线层)是在自动布线时使用,手工布线不需要使用。

对于手工绘制双面印制电路板来说,使用最多的是Top Layers(顶层铜箔布线)、Bottom Layers(底层铜箔布线)和Top Silkscreen(顶层丝引层)。每一个图层都可以选择一个自己习惯的颜色,一般顶层用红色、底层用蓝色、文字及符号用绿色或白色、焊盘和过孔用黄色。

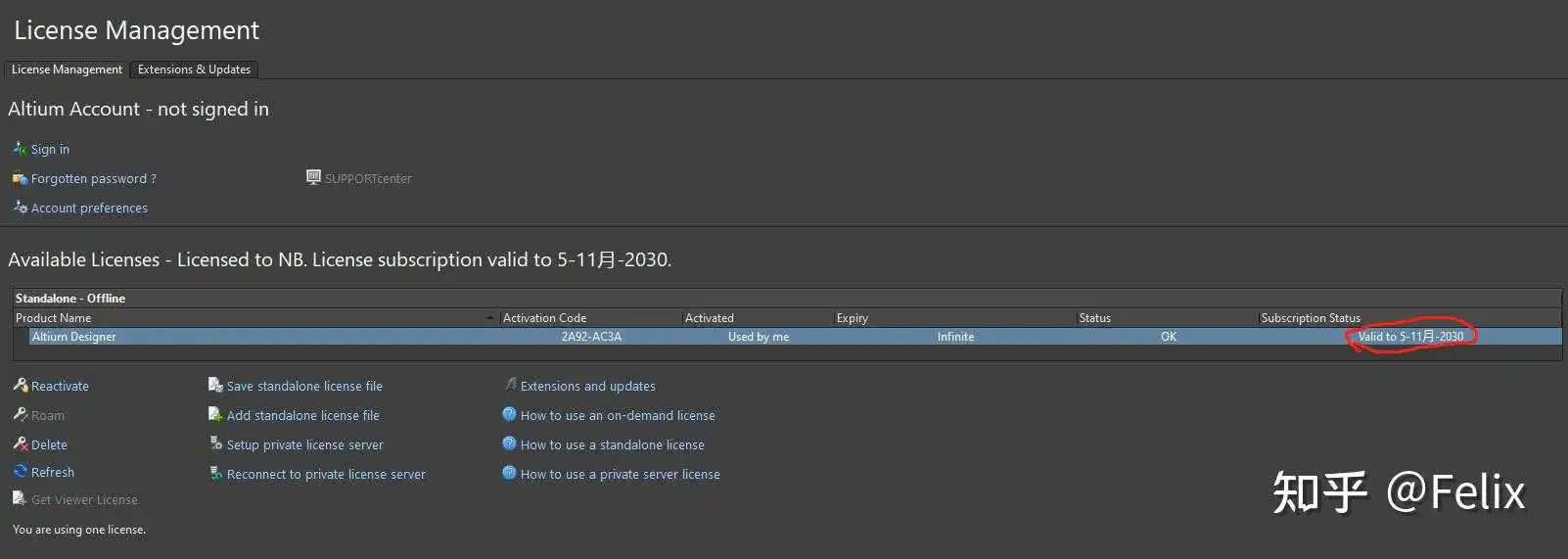

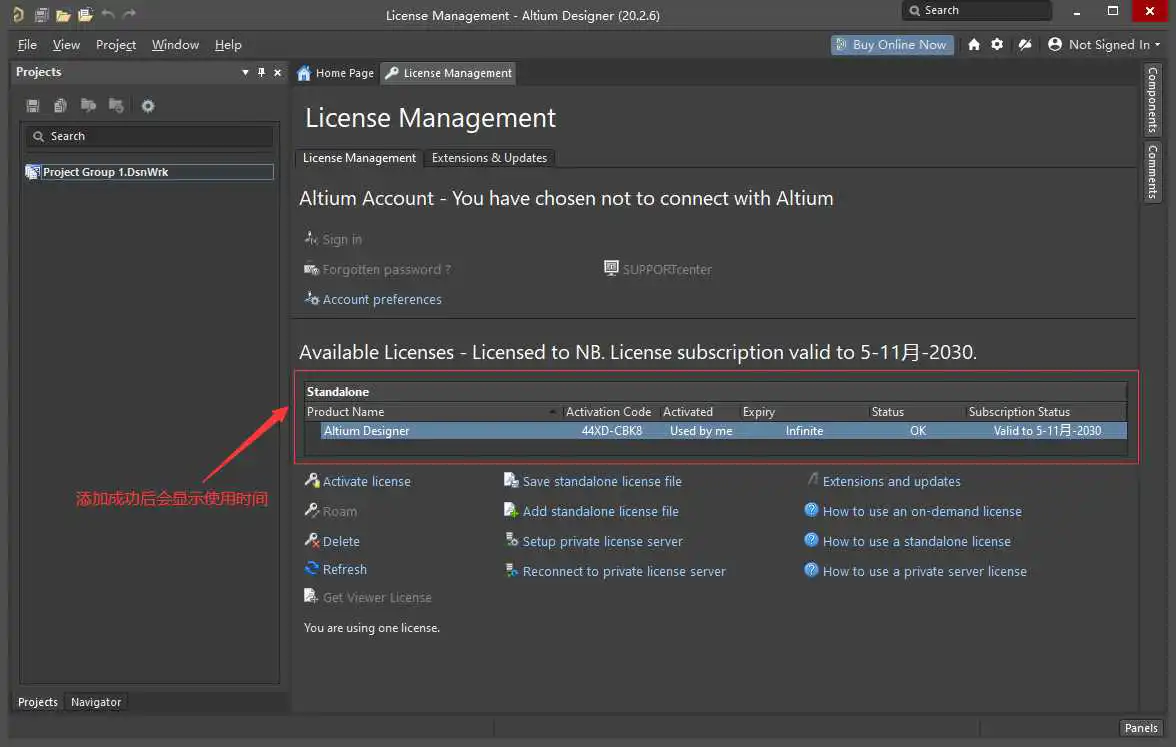

Altium Designer 20安装激活成功教程及汉化流程

Altium Designer 提供了唯一一款统一的应用方案,其综合电子产品一体化开发所需的所有必须技术和功能。Altium Designer 在单一设计环境中集成板级和FPGA系统设计、基于FPGA和分立处理器的嵌入式软件开发以及PCB版图设计、编辑和制造。并集成了现代设计数据管理功能,使得Altium Designer成为电子产品开发的完整解决方案-一个既满足当前,也满足未来开发需求的解决方案。

声明:本安装教程仅供个人之用,请勿用于商业用途。

一、软件安装配置要求

1、硬件配置:

(1)至少 1.8GHz 微处理器;

(2)1GB 内存;至少 2GB 的硬盘空间;

(3)显示器屏幕分辨率至少为 1024×768,32位真彩色,32MB 显存。

2、系统配置:

(1)64 位操作系统,不支持 32 位系统。Windows 7、Windows 8、Windows 10

二、软件安装

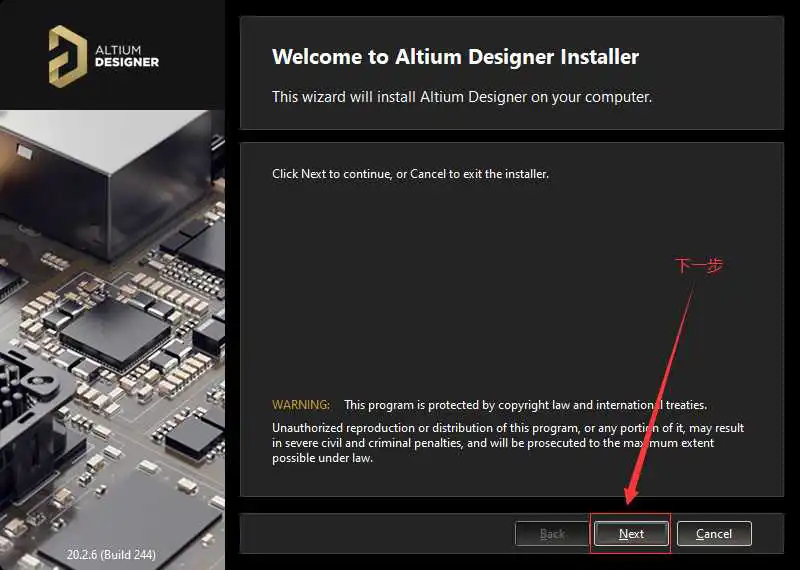

1、准备好Altium Designer 20软件包、shfolder.dll文件和License。解压Altium Designer 20软件包,双击红色框选文件, 即可弹出安装向导对话框,点击next。

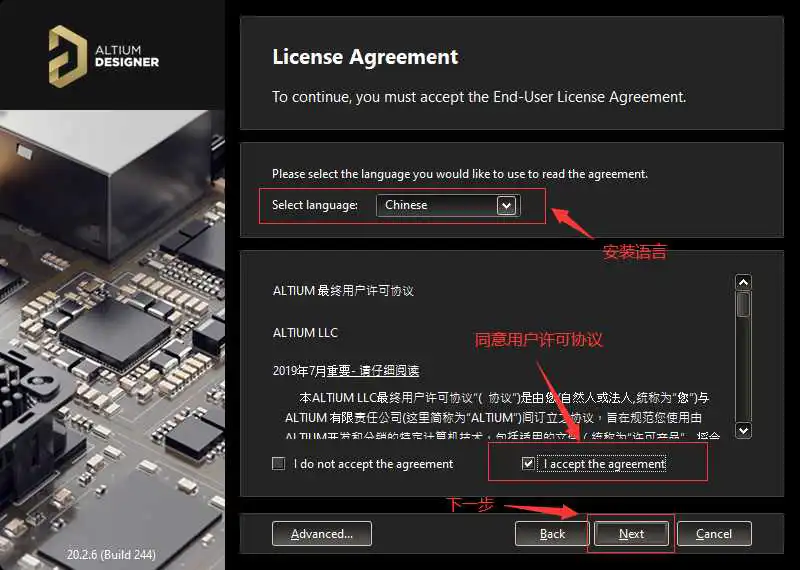

2、选择安装语言为了方便后续操作建议选择中文,勾选用户许可协议。

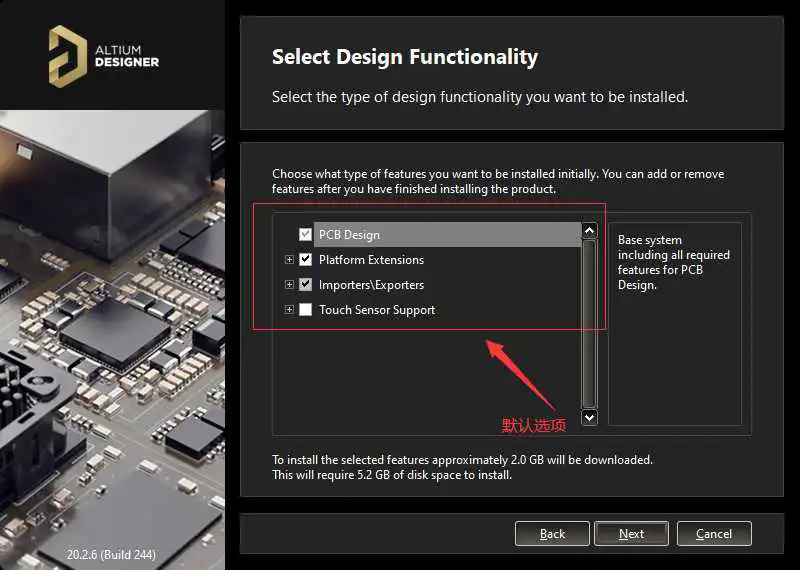

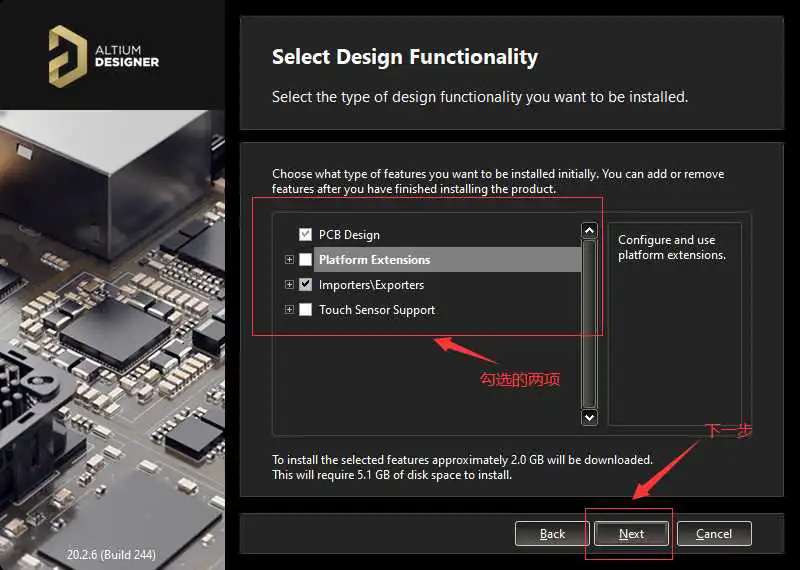

3、显示如图所示安装功能选择对话框。

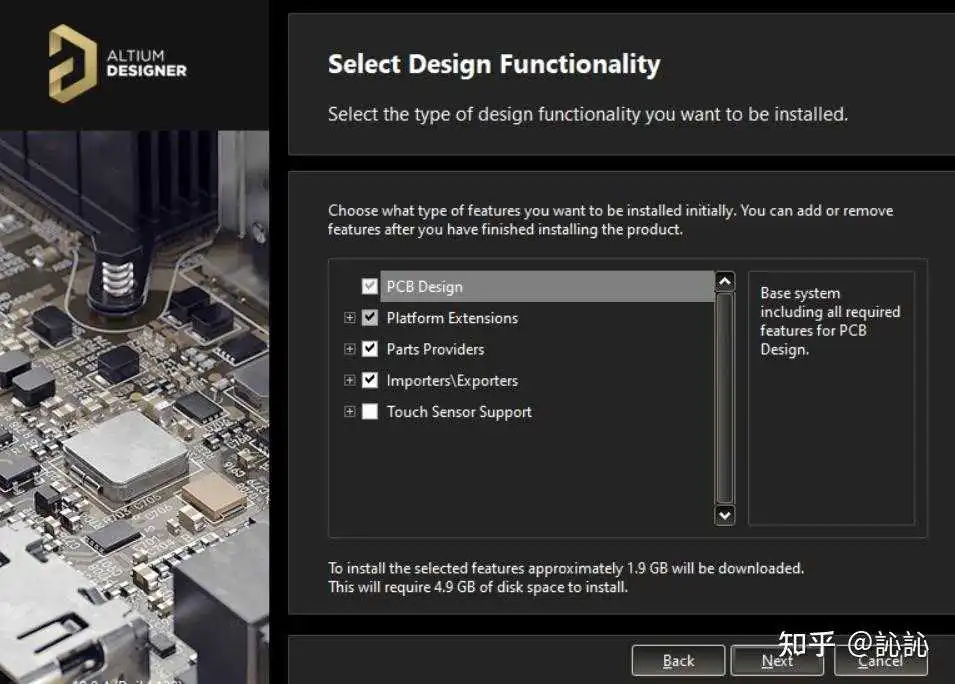

没有特殊要求选择安装PCB Design、 Importers\Exporters 两项即可,或者根据默认值安装也是可以的。

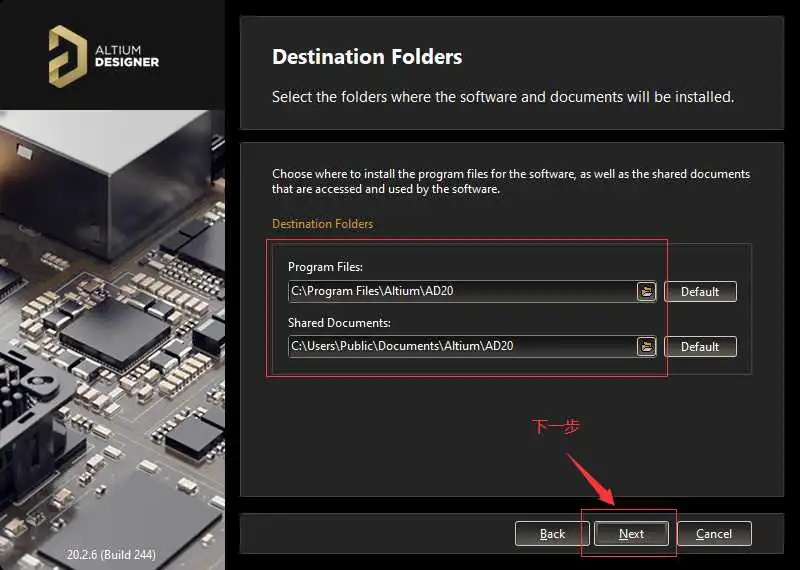

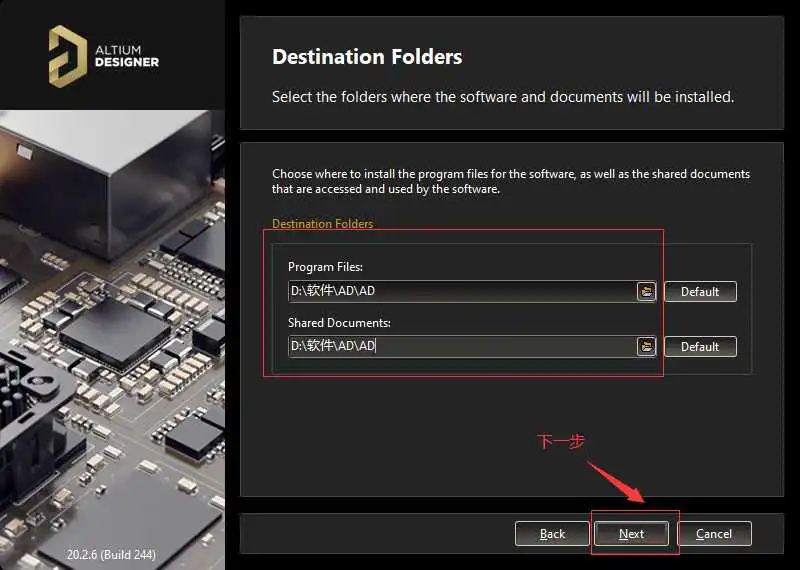

4、如图所示选择安装路径对话框,选择安装路径和共享文件路径。备注:推荐使用默认设置的路径,C盘文件过多可安装在别的盘。

默认路径:

更改后路径:

5、等待安装完成。

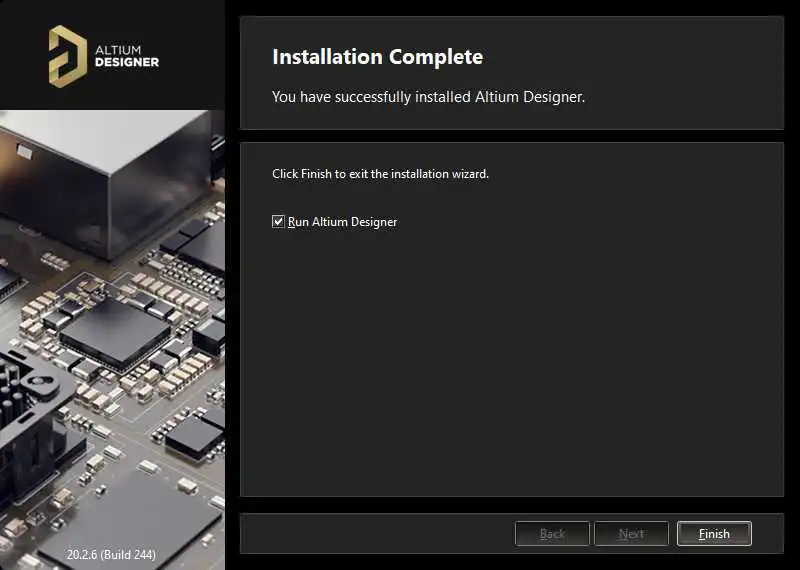

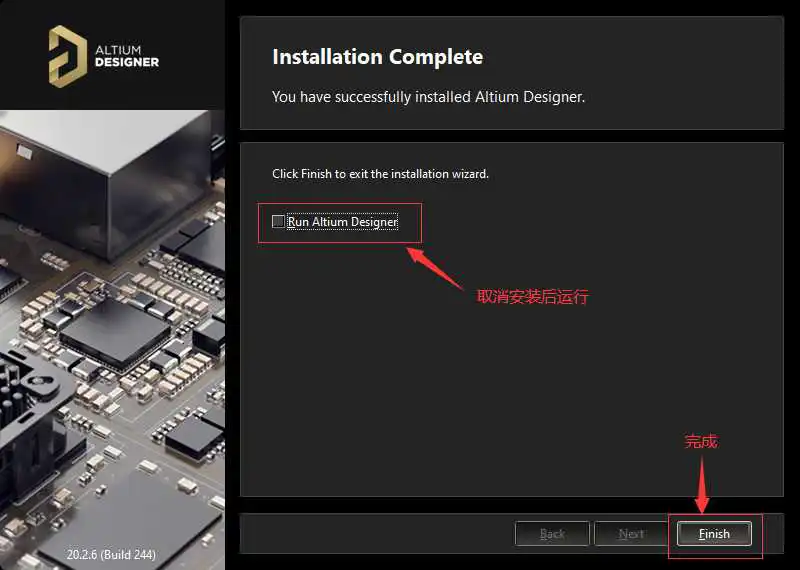

安装完成后弹出窗口,取消安装后运行。温馨提示安装完成后请不要启动软件!!!!!

二、激活成功教程软件

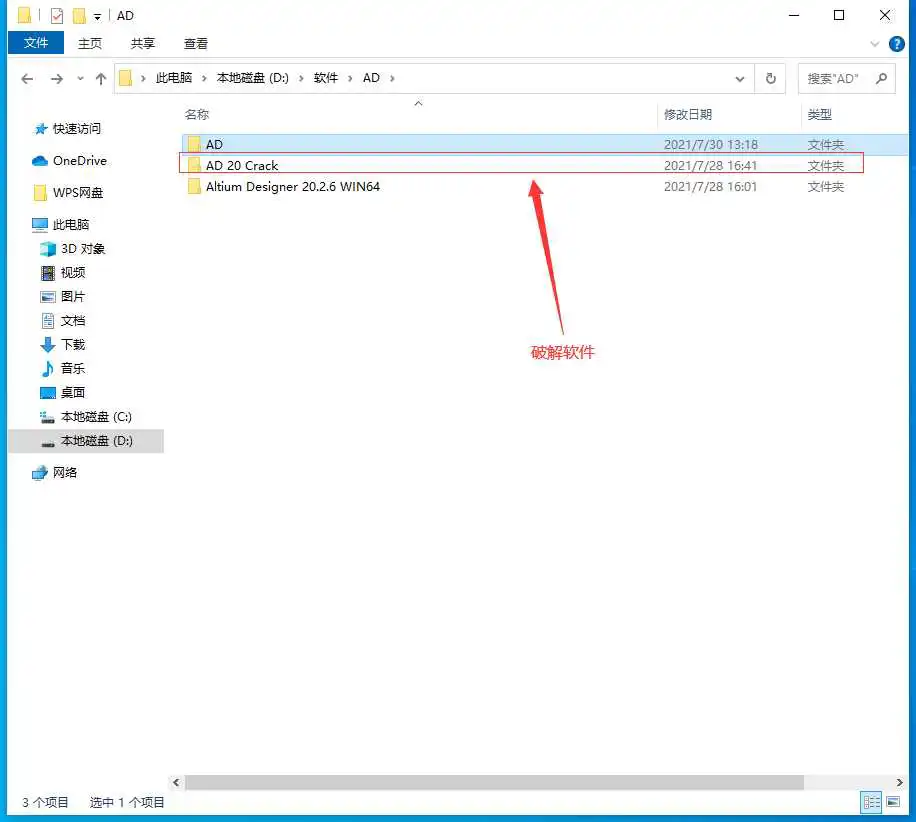

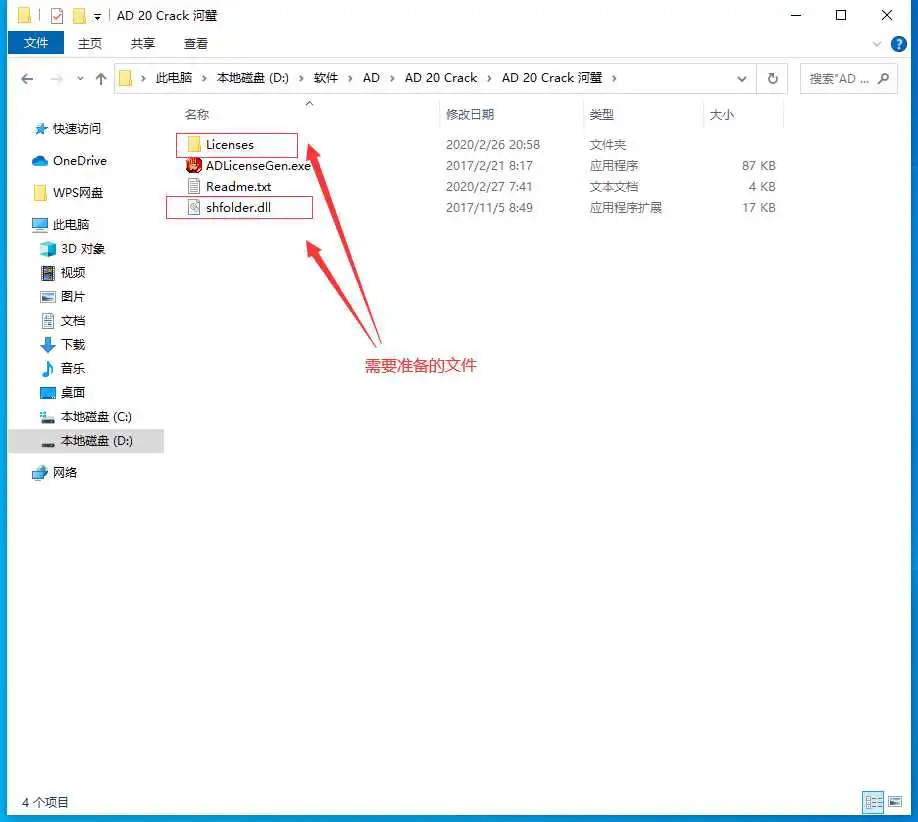

激活成功教程文件准备:shfolder.dll文件和License

1、把shfolder.dll文件复制并粘贴到安装目录中下。

默认路径:C:\Program Files\Altium\AD20

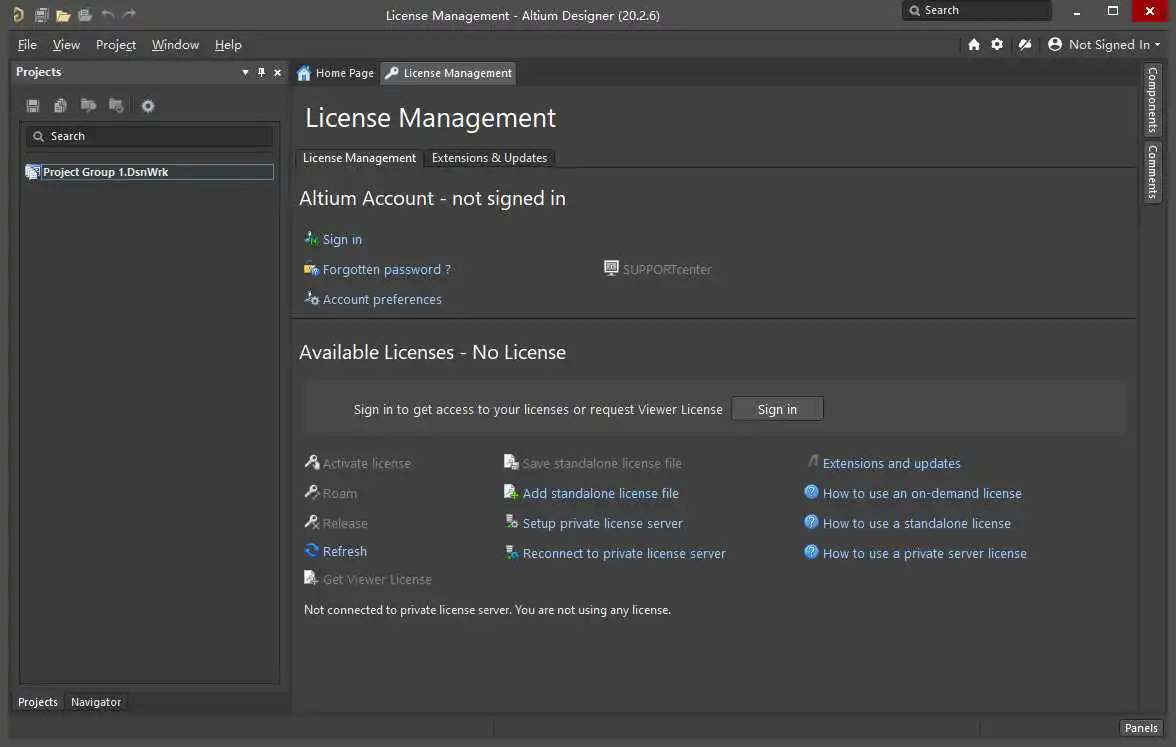

其他路径:安装时选择的路径。

安装目录找到“X2.exe”文件,双击打开Altium designer20软件建议在复制的时候关闭杀毒软件。

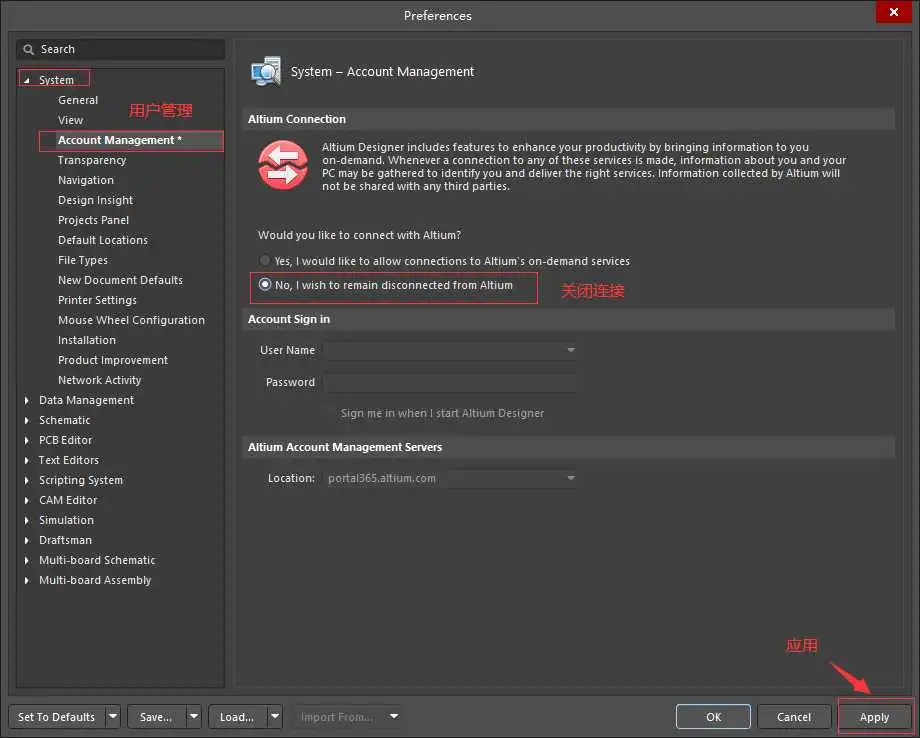

2、打开软件后关闭软件连接,避免出现账号错乱。

3、添加license。

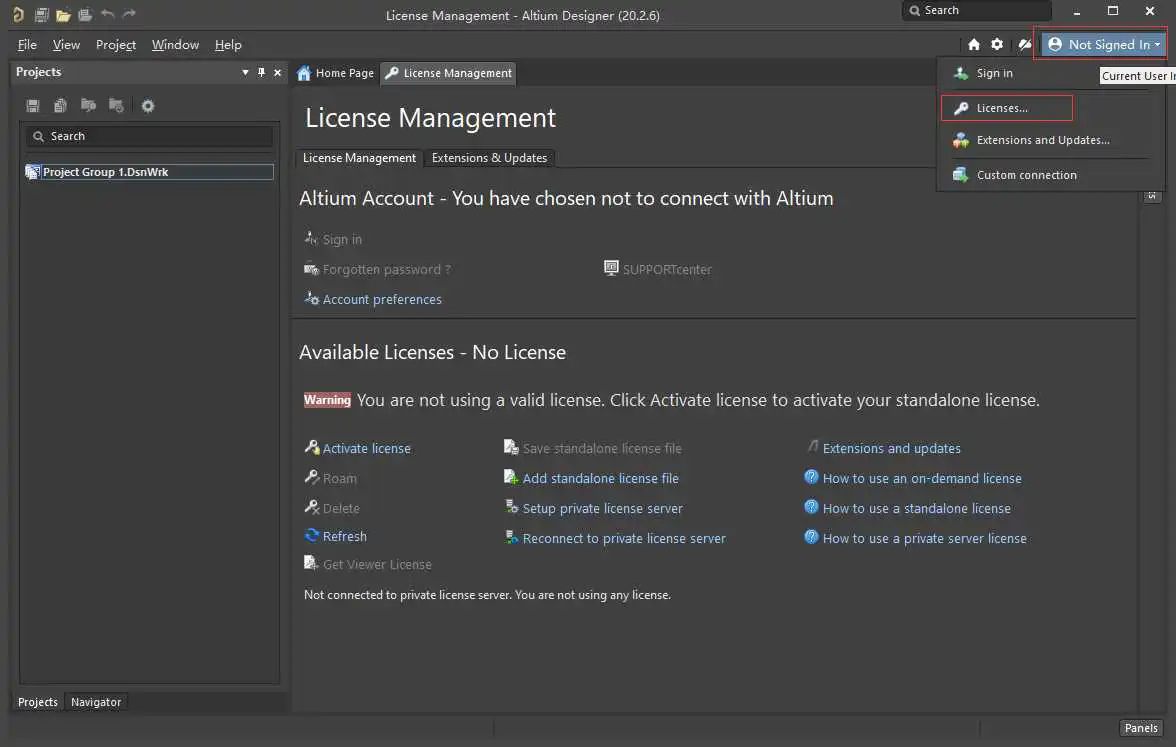

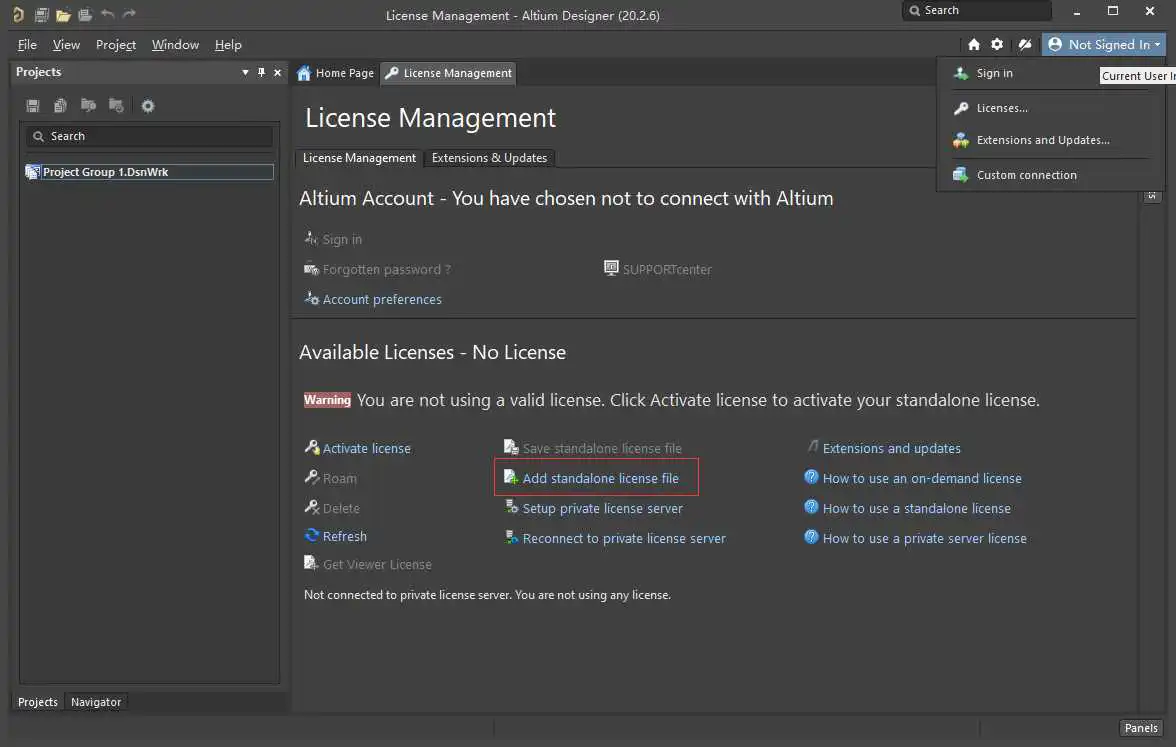

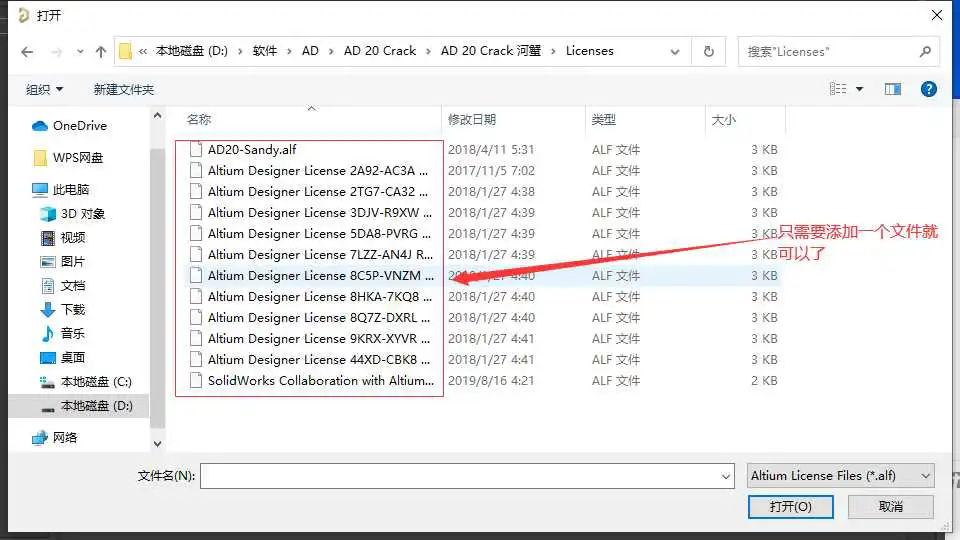

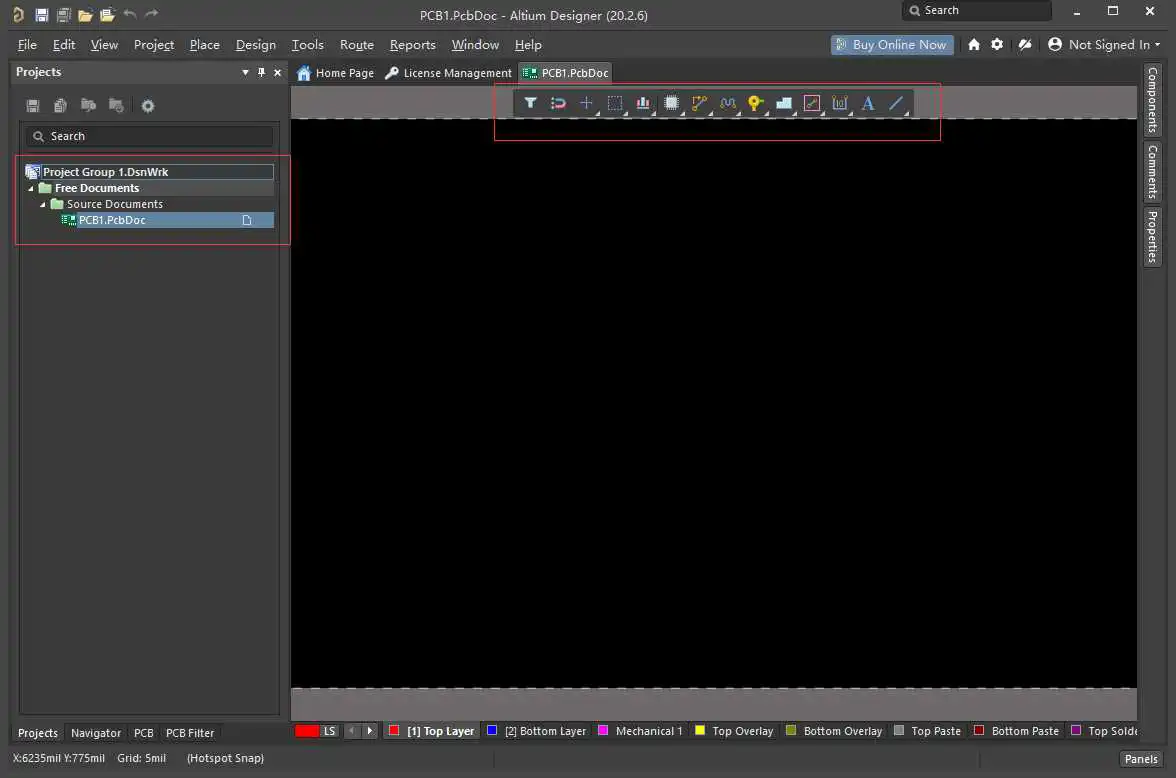

4、检验是否添加成功只需要创建一个新PCB文件,如果安装成功就可以打开并使用。(如图所示软件激活成功教程成功)

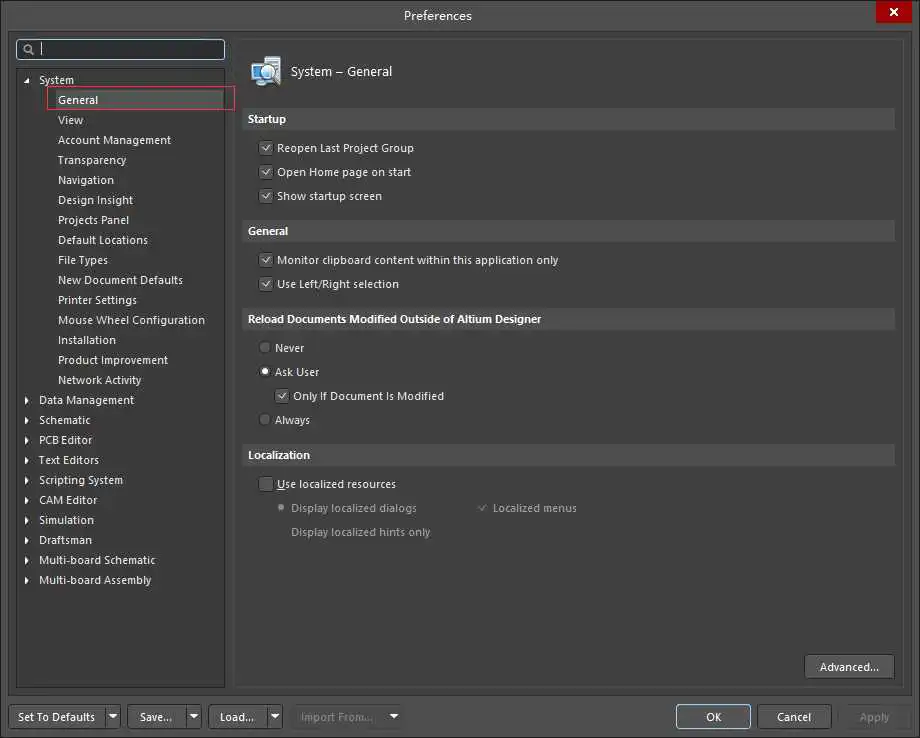

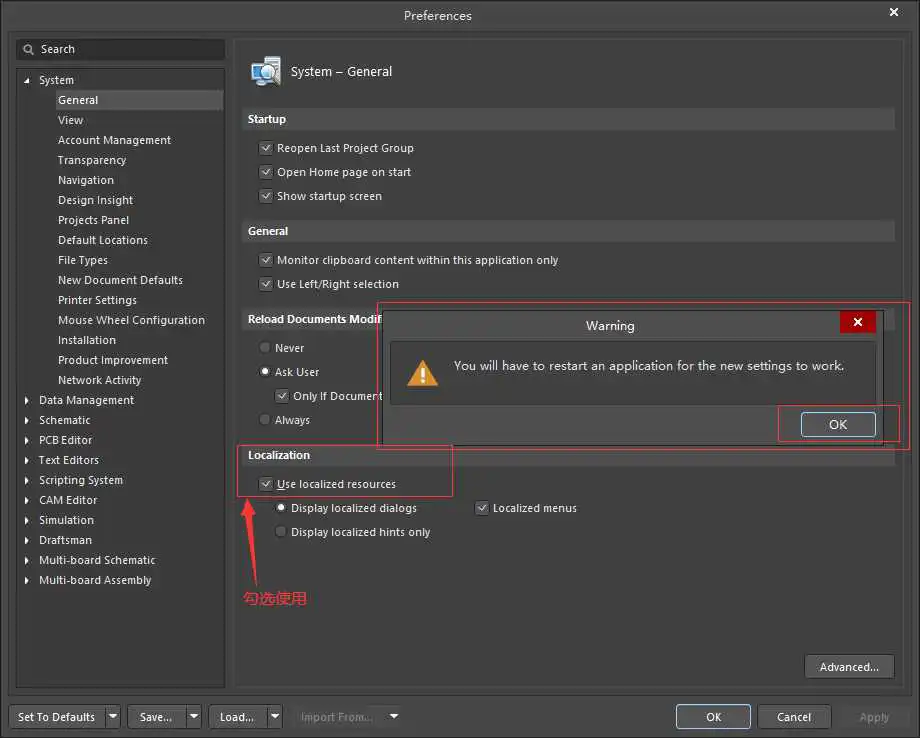

三、软件汉化

1、打开设置窗口。

2、再次重启软件会看到软件已经汉化。

需要软件包和激活成功教程文件的小伙伴可以给我私信哦,留言我每次都忘记看了,老年人请原谅!!!!

之前写了一篇关于AD的使用心得,反响还不错,而且还有意外收获hhh。感兴趣的小伙伴可以去看往期的文章,链接如下。

其遇:相见恨晚的AltiumDesigner使用技巧

首先声明下,写这个专题的目的不是为了做教程,所以前提都是建立在大家对于AD比较熟悉的基础上,旨在为大家减少一些画板过程中的繁琐机械的劳动~废话不多说,正文开始!

这个相信大家肯定都遇到过,举一些栗子就清楚了

- 在导入原理图的元器件的时候,每次都会导入Room,每次都需要删掉Room。或者是在导入的时候取消勾选room的导入

- 丝印文字的默认大小太大,每次都需要手动修改丝印文字的大小

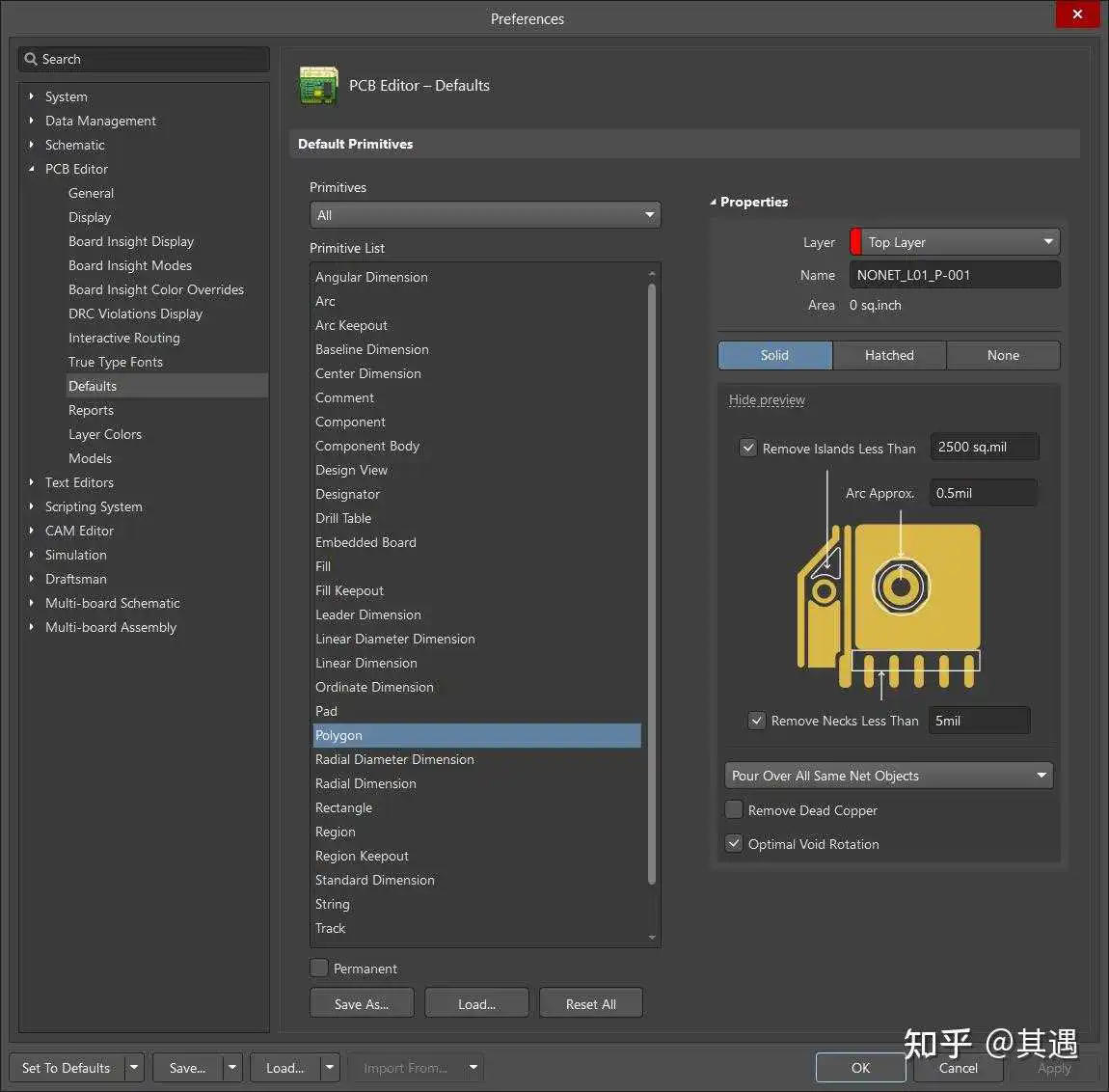

- 关于Polygon的一些默认属性非常坑爹,每次都需要手动修改,比如说Pour Over Same Net Polygons Only需要改成Pour over all same Net Objects,以及去除死铜有时候想作为默认的设置。但是默认的参数不是我们想要的就导致每次都需要修改。

- 默认的string的字体太难看了,每次都需要手动修改

- Via过孔默认是露出铜的,有的人(比如说我)就喜欢过孔盖油,避免不必要的短路

以上的问题或多或少可能大家都遇到过,我以前也是深受这些无用功的影响,导致浪费了很多时间,其实以上的问题都是可以修改软件的默认属性来修改的,只不过都藏得很深,不太好找。这次我就来教大家如何一劳永逸吧!

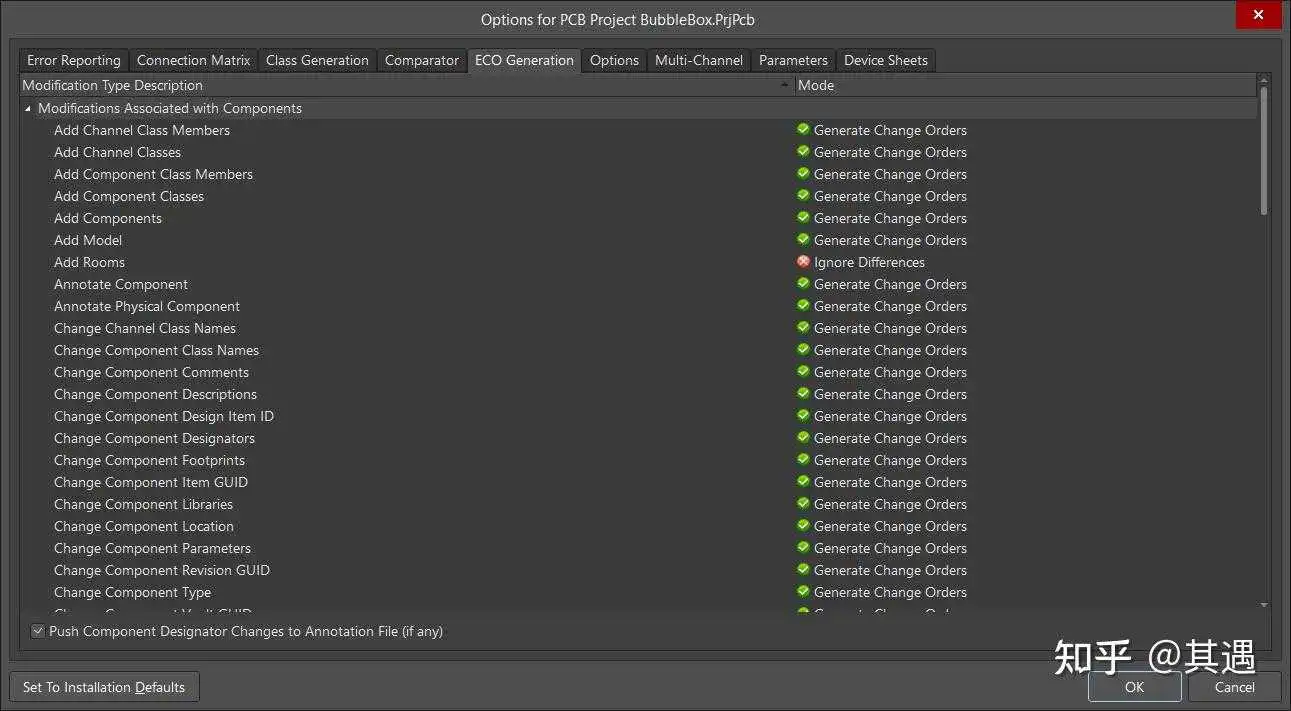

首先第一个问题和后面的方法不太一样,原理图导入到PCB是一次同步的过程,AD会进行Engineering Change Order (ECO) 检查,如果不一致,就提示用户进行同步。AD中认为一张Schematic就是一个Room,所以每次重新导入的时候都会重新将Room导入。而这个导入的过程的修改就在Project-ECO Generation,在这里可以自定义哪些操作是有效的,哪些是可以Ignore的,找到Add-rooms,将其Mode修改为Ignore Differences即可。

剩下的问题,都是类似的问题,都是在修改对象的默认属性。操作方法为,点击Tools-Preferences,然后在左侧找到PCB Editor下面的Defaults。然后右边的列表就是所有AD中的对象的默认属性了,比如下图是修改Polygon默认属性的界面。

其他修改我就不一一说明了,总之这个地方的设置我个人认为很重要,按照自己的喜好设置完了之后神清气爽。

老规矩,举一些栗子

- 布线的时候有时候能对准pad中心,有时候对不准,总有一种AD不听我使唤的感觉

- 有时候布线会推着其他线走,有时候无视规则直接穿过去,有时候又很怂,该走的地方不走。

- 布线希望可以直观地看到还有多少空间可以供我走线

- 走线过程中希望切换粗细

可能有的老司机已经对于这些比较熟悉啦,我个人觉得这几个是对于画板子益处多多,掌握这几个技巧我觉得基本也就满足了基本的需求。

首先是对准pad中心,操作如下图所示,快捷键位shift+E。大家可以看到我在按下shift+E之后左下角是有Hotspot Snap的字样的,这个快捷键就是切换不同的吸附模式(不吸附、吸附到所有层、吸附到当前层)。

然后是切换走线的模式,快捷键为shift+r。大家看图片的最底部的文字,实际这个快捷键就是在不同的走线模式下进行切换。

我们希望在走线的时候看到有多少空间,可以使用快捷键ctrl+w,如下图所示。

切换走线的宽度快捷键为shift+w,可以灵活地在一些预设的走线中进行切换。

这个问题其实上个文章有写过,但是我觉得那个办法还不够完美,还有更方便的办法。废话不多说,直接看图。

这个操作我非常喜欢,首先需要打开交互式设计,然后在原理图中对要布局的模块进行框选(此时PCB视图中相关的元器件就会被选中),然后进入PCB视图,选择

Tools-Component Placement-Arrange within Rectangular

最后在要放置的位置画一个框表示界限,之后AD就会自动布局你的元器件了,是不是很方便~如果是使用上一次的方法的话,元器件是一个一个蹦出来的,还需要手动进行摆放,而这个则直接按照区域给你排列好,非常方便。

同样,建议大家将这个操作搭配快捷键进行使用,爽到飞起~

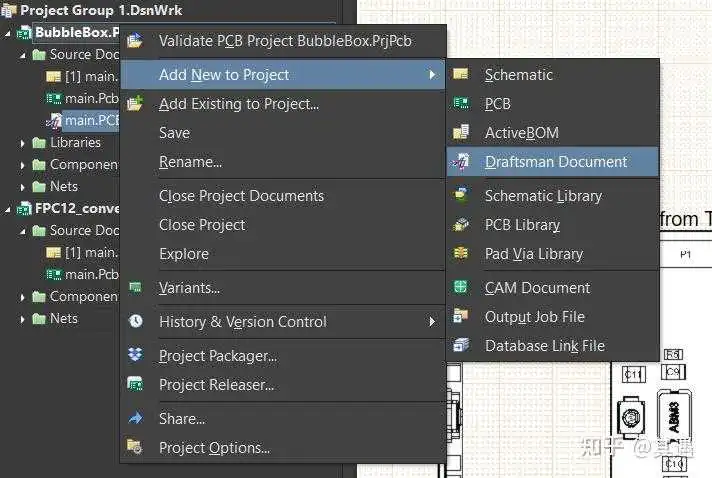

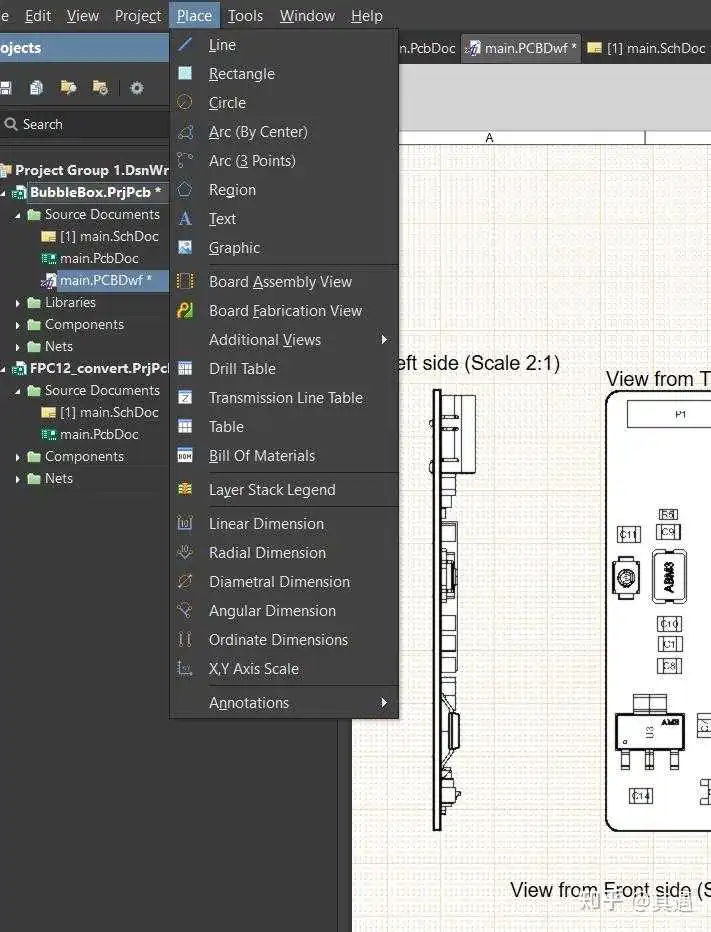

这个功能是我最近找到的,既可以导出3D模型(当然这个功能也可以通过3D视图里面截图实现),还可以导出轮廓图(包括各个视角)并且显示每个原件的标号,这个是不是很方便手工焊接的时候找元器件呢?(尤其是在元件比较小,我们隐藏了designator的时候)

创建这个视图,首先需要创建一个Draftsman的文件。然后保持默认的参数,直接点确定。

然后选中这个Draftsman文件,点击Place。

其中

- Board Assembly View 就是装配视图,也就是轮廓图。然后可以在右侧属性中设置比例、视角等等

- Board Fabrication View 就是做出来的板子的视图,没有元器件的那种

- Addtional Views 里面还有很多有趣的视图,大家可以去探索呀~

然后大家就可以按照你想导出的类型来自己发挥了!

先写到这里吧,预告下期可能会写关于模块化Layout的教程(如果大家感兴趣的话,先定个小目标,点赞过50)。所以,如果大家喜欢的话,麻烦点赞加收藏关注三连一波~

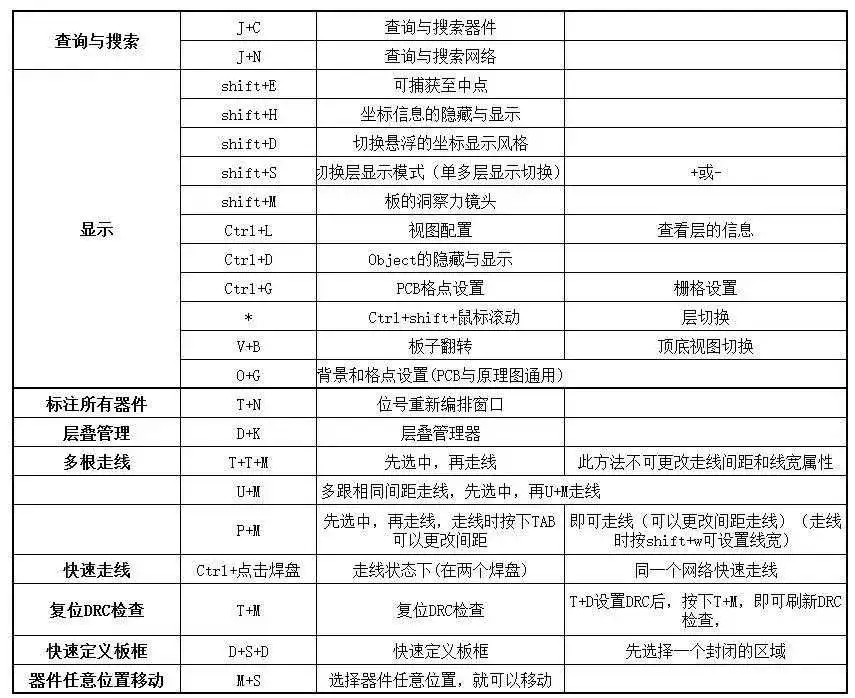

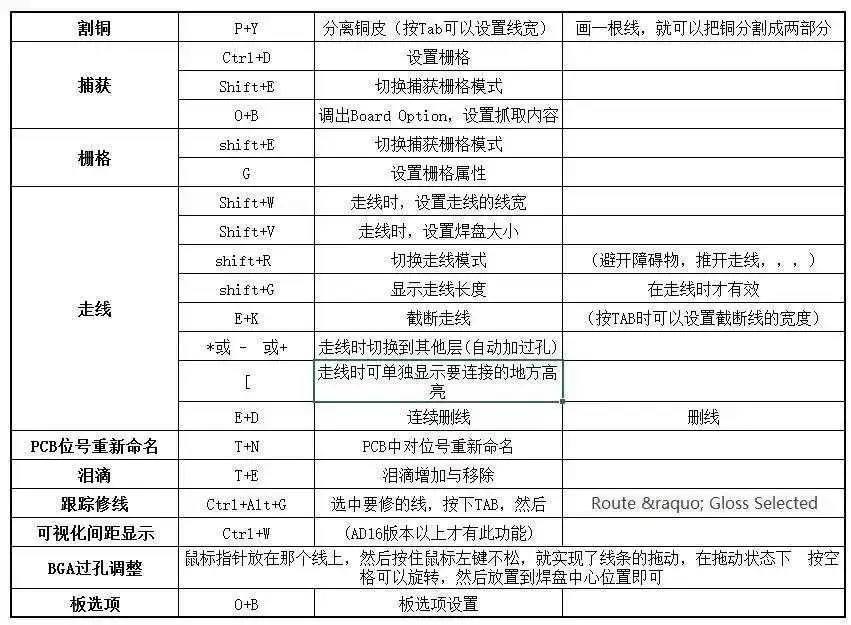

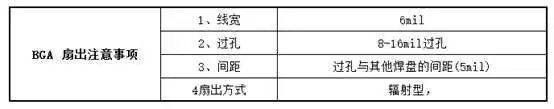

AD常用快捷键总结

1:shift+s 键 切换单层显示

2:q(Ctrl+Q)英寸和毫米 尺寸切换

3:D+R进入布线规则设置。其中 Clearance 是设置最小安全线间距,覆铜时候间距的。比较常用

4:CTRL+鼠标单击某个线,整个线的NET 网络 呈现高亮状态

5:小键盘上的 * (星号键)可以在top、bottom layer切换,达到快速切换上下层。另外 + - 可以把所有显示的层轮流切换。

6:CTRL+SHIFT+ T 、B、L、R 可以快速对齐所选中的元件 上 下 左 右。

7:M+I 可以把选中所有的元件,翻转过来。这样可以在上下层切换,方便布线,调整印丝层。 很实用的一个操作。

8:如上所述,还可以 查看板子底部,就点击 查看 翻转板子 板子就反过来,但是属性还是 一样。只是从板子底部看了。

9:器件联合 选中两个器件 然后右击 选择 联合-从选中的器件生成联合 这样可以操作两个位置在一起的器件

当要去掉时候 选中器件 右击 联合-从联合打散器件 那么连接在一起的就能够单独操作了。

当选中联合的器件,右击选择联合,有个 选择所有的联合 这样一下子选择所有联合的器件。固定的外框就可以联合起来移动操作。

10:多根线同时画的时候,每个先画个短的线,按SHIFT 选中所有一起画的线,选好,松开SHIFT. 鼠标移动到线头 白点处,然后拖动,那么所有线就一起拖动。 转弯一次,松开, 在拖,又可以转弯。

11: 快捷键 t c交叉探针 看到寻找 原理图 和 PCB 的元件位置 选下,然后跑到PCB 就能看到原理图那个元件的位置。

12: ed 删线

13: 捕获焊盘 查看——网格——切换电气网格(shift + E)

方格与格点的切换:View-Grids-ToggleVisible Grid Kind

原点:Edit-Origin-Set

边界的定义:Keep Out Layer-Utility Tools-Place Line 按TAB可定义线宽

选取元件:PCB-PCB Filter-IS Component

逐个放置元件:TOOLS-Component Placement-RepositionSelected Components

自动布局:ToolS-Component Placement--Arrange Within Room

自动布局器:ToolS-Component Placement--Auto Placer

元件排列:选中元件右键Align- 或Alignment Tools--

元件在层之间的快速切换:拖动元件的过程按L键

让焊盘放在格点上:选中元件,右键-Component Actions-Move ComponentOrigin To Grid

移动元件的远近:"G"键 选择mil

刷新屏幕: END

改走线模式:shift+空格键

(“45°线性” “45°+圆角” “90°”“ 任意角”“90°+圆弧 ”“圆弧”)

遇障碍物:右键-Options-Preferences-...

推挤: Shift+R

布线快捷菜单:“~ ”键

线宽设置:“Shift+W”

过孔修改规则:Design-Rules-HoleSize;

板边5mm圆弧:Place-KeepOut-Arc

切换英美单位制度:Ctrl+Q

显示布线快捷菜单:键盘左上角快捷键“~ ”

层间切换:"+""-"

字体(条形码)放置:"A"-Place String;

对板的定义:Designers-Board Shape-R/D;

尺寸标注:Place Dimension-Place Linear Dimension

工具栏恢复原始状态:在工具栏处右键CustomizingPCB Editor-Toolbar-Restore;

填充:Place Fill;

复制粘贴:选中-Edit-Rubber Stamp-单击

粘贴特殊形状:选中-Edit-Paste Special

选择一组Select:“S键”-Touching Liner线/Rectangle矩形

或Shift 一个个选

移动Move:"M"

整体移动:选中-右键-Unions-Create Union fromselected object/break

解脱从联合体

弱小信号线包地:选中-“s”select net,Tool-Outline-Selected Objects

查找相似物体:右键-Find SimilarObject

查看布线层:Shift+F或“*”切换层

切断线:Edit-Slice Tracks

布完线进行规则检查:Tools-Design Rule Check-Run D_R_C_

3D视图:数字键“3”或View-Switch to3D,Shift+右键旋转;

铺铜:Place-Polyon Pour

去死铜:双击铜区,Remove Deader Copper 打勾

原理图和PCB的双向同步更新:

检测PCB与原理图的不同处:Project-Show Differences

在原理图里更改后更新到PCB:Design-Update PCB Document in

在PCB里更改后更新到原理图:Design-UpdateSchematics in

标号Designator显示:PCB FilterISDesignator 然后PCB Inspector Hide

重新标注:Tool- Re Annotate

元器件标号自动排列:选中器件-右键-Align-Position Component Text

补泪滴:Tool-Teardrops,焊盘与导线连接更牢固

生成生产制造文件:File-Fabrication Outputs

生成PDF文件:File-Smart PDF

翻板:View-Flip Board

打开层对话框:L

打开选择:S

跳转:J

英寸和毫米切换:Q

翻转元器件:空格

改变线宽,孔径:选中导线或过孔,同时按下Tab键

选中目标:shift+单击

PCB换层并自动添加过孔:小键盘上的“*”

系统设置:DXP->preferences

其中General--Use localized resources中文

其中Backup :设置备份时间

树形图标:home

快捷键:右下角help-shortcuts

默认布局:View-Desktop layouts--Default

窗口缩回的速度:DXP->preferences->system->view--Hidedelay

打开不同面板:右下角System等等

切换不同窗口:ctrl+tab

放大和缩小:ctrl+鼠标中键滚轴

修改右下方的边框(title,日期)格式:DeSign-Template-Set Template File Name...A4

走线自动延长: Drag---ctrl+鼠标拖动

复制目标:选择目标,按住shift拖动

自动添加元件编号:Tools->Annotate Schematics

Preferences-->Schematic-->Graphical Editing Convert Special Strings 转换特殊字符串

(1) Part Comment ---same Current Footprint ---same ,点击OK按钮

(2) Select ALL

(3) SCH Inspector 窗口 修改 Footprint

Tools-->FootPrint Manager

分层设计

(1)一种水平设置,N个分图 ,net设置全局(project-->project options-->http://www.wenkuxiazai.comIdentifier Scope..Gloal) 不推荐

(2)一种垂直设置

,一个总图(Sheet Entry),N个分图(PORT) 连接只能Sheet Entry到PORT

第二种方法:

(1)Place sheet Symbol(方框) 和sheet Entry(放在方框边界内侧)

(2)选择sheet Symbol,右键选择"Sheetsymbol actions"--creat sheet from symbol

原理图库

(1) File-->New-->Library-->sch..

(2) 右边下方SCH打开SCH Library

窗口

(3) Place->RecTangle,注意放在原点

(4) Library Components Properties

Designator U?

Comment max232

Symbol Refernece max234

(5) 可将一个元件库分为两个Part,例如parta,partb(通过Tools-->new part)

特殊用途:选择该元件,按F1打开该元件的pdf文档

Library Components Properties-->Parameters for Component -->Add..

Name: HelpURL Value: C:\zy\abc.pdf#page=5

PCB库

(1) File-->New-->Library-->pcb..

(2) 右边下方PCB打开pcb Library 窗口

集成库

(1) File-->New-->Project-->Interger Library

(2) 新建sch.lib和pcb.lib, 在sch.lib中选择Tools-->Model Manage....

(3) Project-->Compile Integrated Library

盲孔(BIINDVIA):从印制板内仅延展到一个表层的导通孔。

埋孔(BURIEDVIA):未延伸到印制板表面的一种导通孔。

PCB绘制

(1) 在PCB中 Design-->ImportChanges From.....

(2) S+N 选择相同net的线

(3) Design-->Board layers & color-->show/hide polygons hide (将覆铜隐藏) (L快捷键)

(4) 查看PCB元件,通过打开PCB窗口,选择Components

(5) shift+S 单层打开或关闭

(6) 对弱小信号可选择包地处理(Tools-->Outline Selected Object)

(7) Tools-->Design Rule Check...

(8) File-->Fabrication Outputs-->Gerber Files

覆铜:

place-->polygon Pour...

1. Pour Over Same Net Polygons Only 相同net铜箔覆盖

2. Pour Over All Same Net Objects 铜箔覆盖相同net部分(将相同net的导线等等融合了)

注意 :如果要保存为PCB4.0 Binary File(*.pcb), 覆铜要选择网格式,(可将网格Track With和GridSize设置一样,就如同Solid格式了)

如何隐藏所有Designator(即u1,r1,r2....)

(1) PCB filer-->IsDesignator 选择所有Designator

(2) PCB Inspector-->Hide

如何将Designator(即u1,r1,r2....)自动放置在元件附件

(1) PCB filer-->IsComponent

(2) Align-->Position Component Text....

将PCB翻转 查看反面方便 view-->FilpBoard

PCB查看层数 Design-->Layer Stack Manager

"类" Design-->class

比如新建一个net class ,把Vc3.3 VC5等加入,然后在rule中选择Net class,这样规则适用范围就是自己定义的类了

按键2--2D 按键3--3D

原理图画线:P+W

PCB图画线: P+T

在原理图里同快速查找元器件:CTRL+F

在PCB里面快速查的元件:J+C

选择net: ctr+H或S+N

去掉全部选中物体:E+E+A

删除两个焊点间的导线:T+U+C

单层打开或关闭:shift+S

去掉过滤:shift+C

在交互布线的过程中,切换布线形状:Shift+空格键

拖动时连线跟着延长:ctrl+鼠标左键拖动

PCB选择相同net,并高亮:ctrl+鼠标右键

hide/show层:ctrl+D

原理图和PCB快速切换:ctrl+crosspobe

分图和总图的切换:ctrl+上下箭头

测量距离:ctrl+M

放弃上一步操作:Backspace键

一、PCB中常用快捷键

R+L 输出PCB中所有网络的布线长度

Ctrl+左键点击对正在布的线完成自动布线连接

M+G 可更改铜的形状;

按P+T在布线状态下,按Shift+A可直接进行蛇线走线

T+R对已布完的线进行蛇线布线

E++M+C点击空白出可迅速找到PCB上想要的元件

Backspace 撤销正在布线的上一步操作

* 切换布线层,可在布线过程中放置过孔

Ctrl+Shift 切换层并放置过孔

F8/E+O+S设置圆心点

M+I 翻转选中的元件

P+T 布线

T+E 补泪滴

P+G 铺铜

S+Y 单层选择线

E+B 选择进行复制

三、BGA 扇出注意事项

四、常见的单位换算

很不幸,又一个朋友中招了,如期收到Altium Designer的法务函。类似下面这个经历:

AltiumDesigner的法务函,今天你收到了么?

她们公司实际上并没有用Altium Designer,她甚至都不知道这是干啥的。她们9月份刚招了几名实习生,实习生出于热心给他们改进了设备的自动测试系统,要画电路板。于是实习生下载了Altium Designer这个在学校被普遍使用的D版软件。

这系统还没有彻底调完善,法务函就来了!

据说Altium Designer的工作人员还热心的打电话过来询问使用情况、效果如何,态度充满了恐吓和威逼。她压根儿就不知道这是啥,通过Altium Designer的工作人员介绍,她才知道是电路板设计软件。

经过一番询问才知道是实习生用的,她们可是在宝安区备受关注的一家成长企业,生怕自己屁股不干净。今天早上给我打电话来了……

我的建议是:你要是还没有形成销售,产品就别上线了!没有形成销售收入这个事实先确立下来。然后把那台电脑趁早送人,比如送给我。然后就不要再理对方了。法务函不是法院传票,对方要是证据确凿认定你们违法那他们起诉就可以了。说白了,对方就是想让你们买软件。

我还给她建议,如果真的要做电路板,立创EDA是个非常好的选择,一步到位,步步为赢

国产立创EDA - 一个用心为中国人定制的电路板开发平台

背景说完了,说正事儿:如何阻断Altium Designer联网?算是给国内还没有放弃Altium Designer的初创企业及小微企业的同胞们一个弃暗投明的过渡期。(对于有钱的企业,选不选择这款软件那是公司的选择,不做评价。但对于很多初创公司或者小微公司,这十几万甚至几十万的采购可能就能把一个公司掏空。最最关键很多老板是不知道这个软件的销售策略是这样的,都是出事儿后被逼迫购买的)。

至于网上的那些乱七八糟的方式,风险极大,企业就不要去尝试了。

Altium Designer 分为(15、16、17、18、19、20)版本

涉及内容:

- Altium Designer 19 安装

- Altium Designer 19 下载

15、16、17、18、20版本在【版本篇】进行上传(温馨提示:版本易出现闪退,不稳定情况,绘制完记得及时保存)

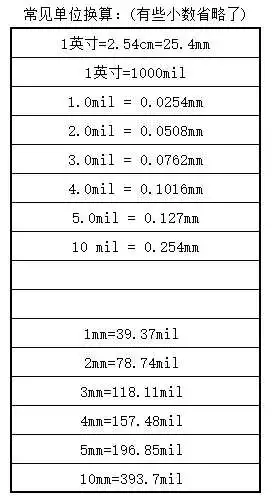

- 首先创建一个文件夹名字为Altium Designer(名字随意),将压缩包放入文件夹中

- 进行压缩包解压

- 找到(安装包)文件夹,打开

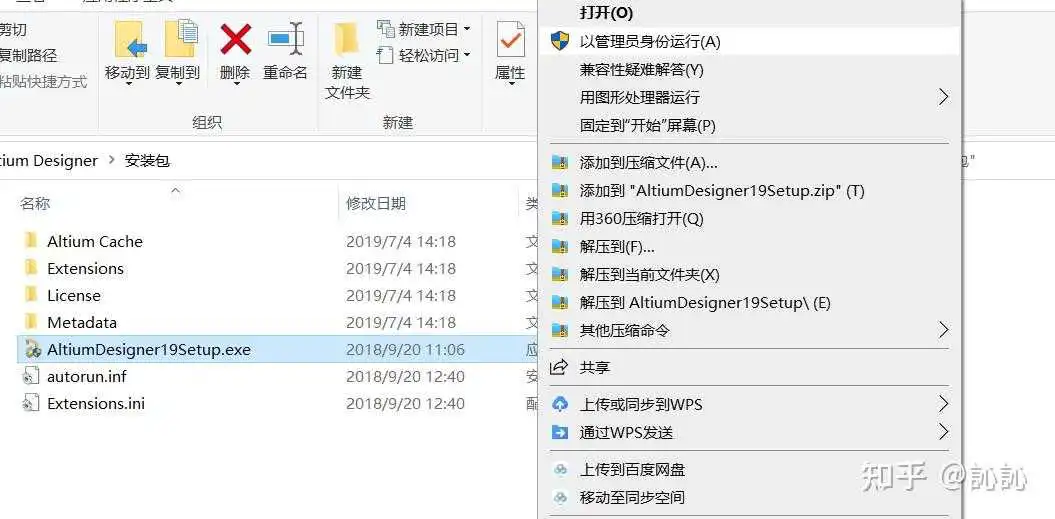

- 找到 AltiumDesigner19Setup.exe 应用程序,点击右键以管理员身份运行

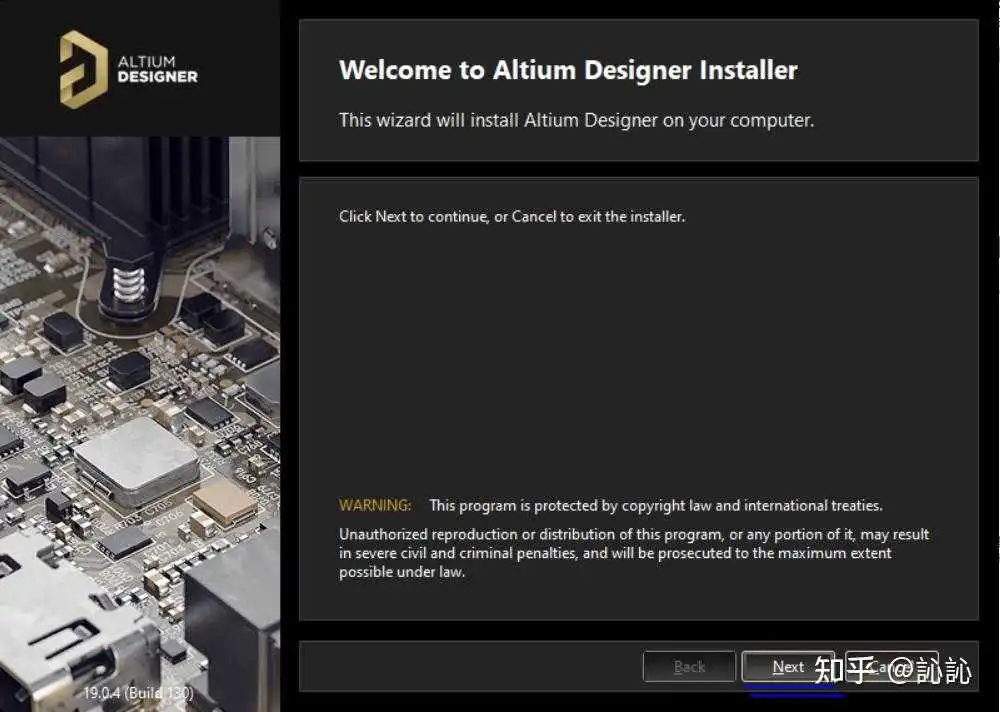

- 弹出如下窗口,点击Next(画横线)

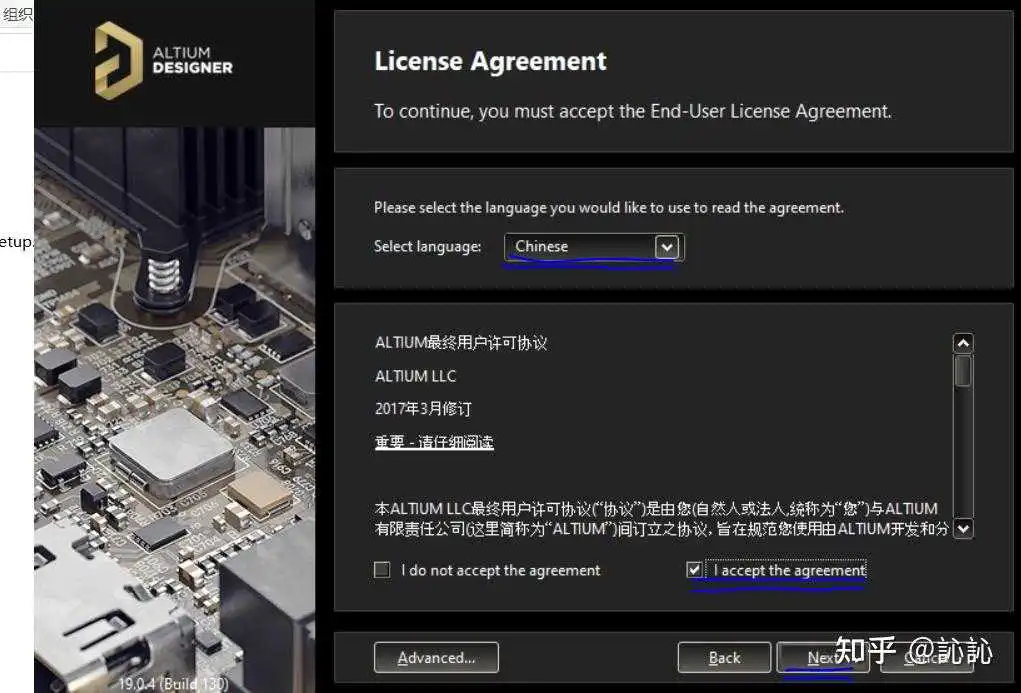

- 在 Select language 中 选择 Chinese,勾选 l accept the agreement, 点击 Next(画横线)

- 弹出如下窗口,点击Next

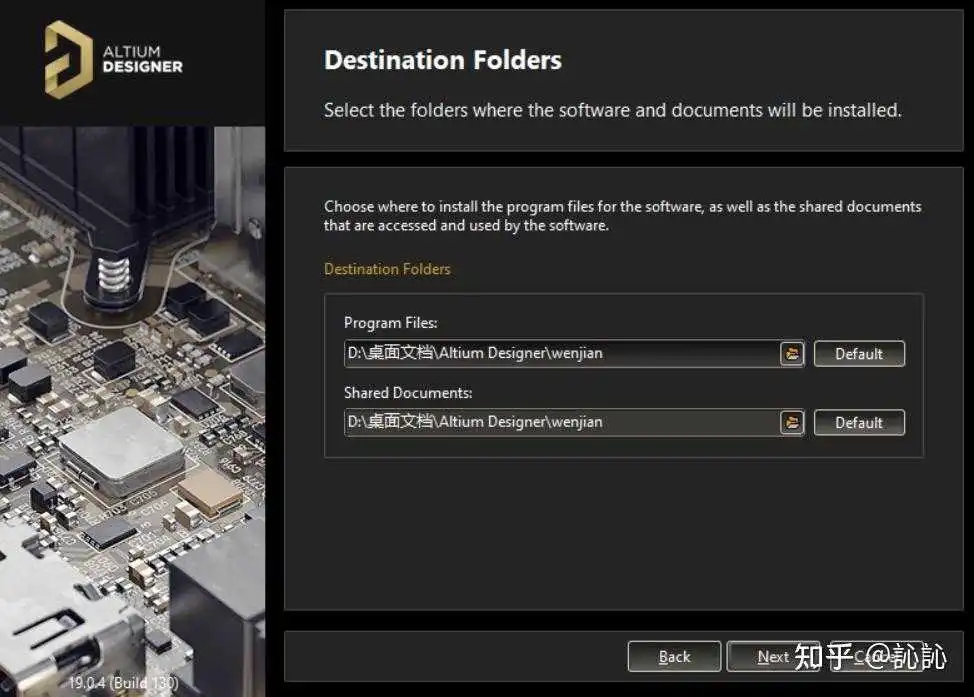

- 弹出如下窗口,然后进行文件路径更改(建议选择除C盘以外【其他盘】,建议先建立一个文档,方便后期查找)

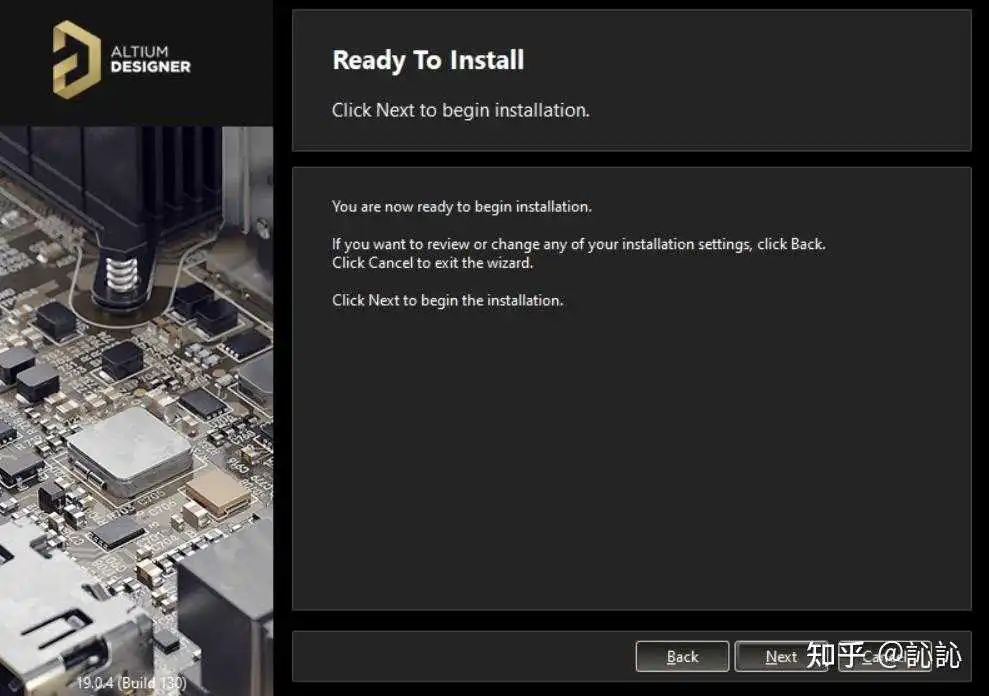

- 弹出如下窗口,点击Next

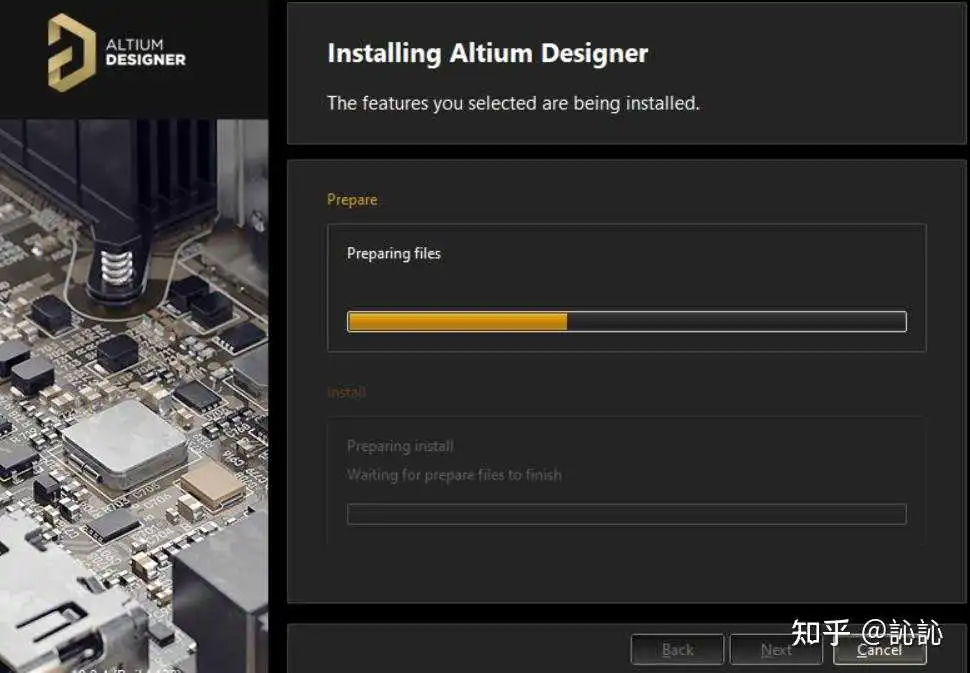

- 安装完成后 ,取消勾选 Run Altium Designer,点击 Finish

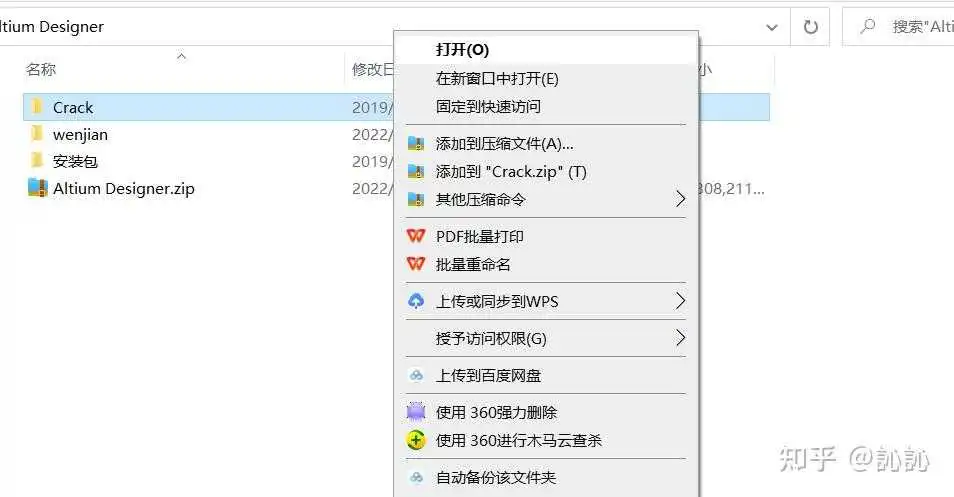

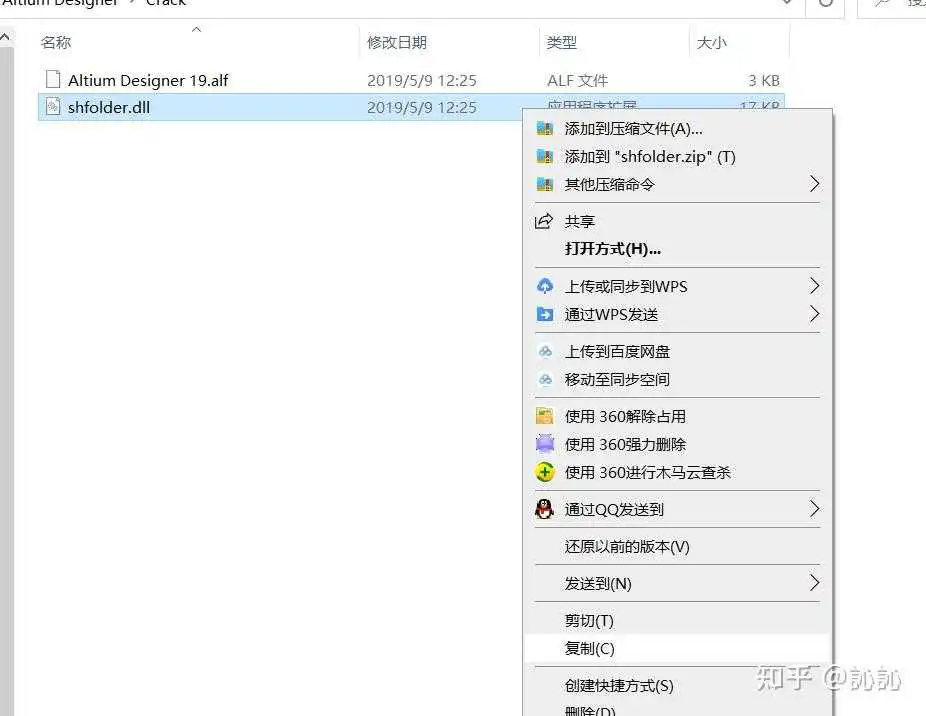

- 在解压包中找到Crack 文件夹打开

- 找到一个名字为 shfolder.dll 的应用程序扩展,点击右键进行复制

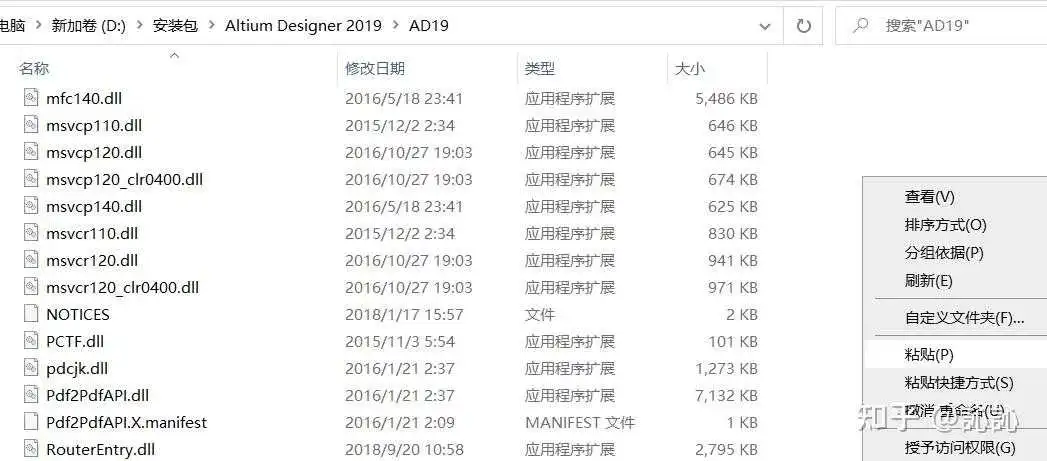

- 创建一个Altium Designer快捷方式,点击右键 ,打开文件所在位置

- 在Altium Designer所在文件夹 D:\安装包\Altium Designer 2019\AD19(具体情况查看自己文件夹),中点击右键进行复制

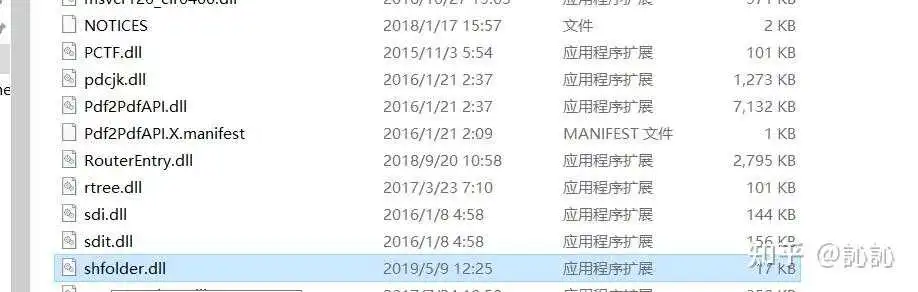

- 查看复制是否成功,出现shfolder.dll 的应用程序扩展,说明复制成功

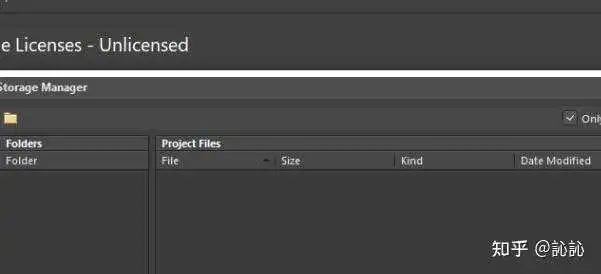

- 双击图标启动软件,出现如下界面,点击OK

- 出现如下界面,点击关闭

- 点击Add standalone license file

- 选择 解压包的文件夹中找到 Crack 文件夹中 licenses 文件夹下的任意一个文件,点击打开。

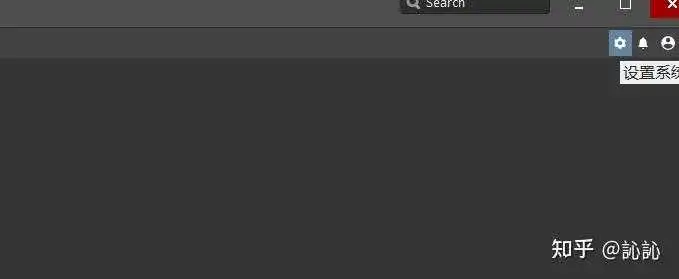

- 点击设置系统参数图标

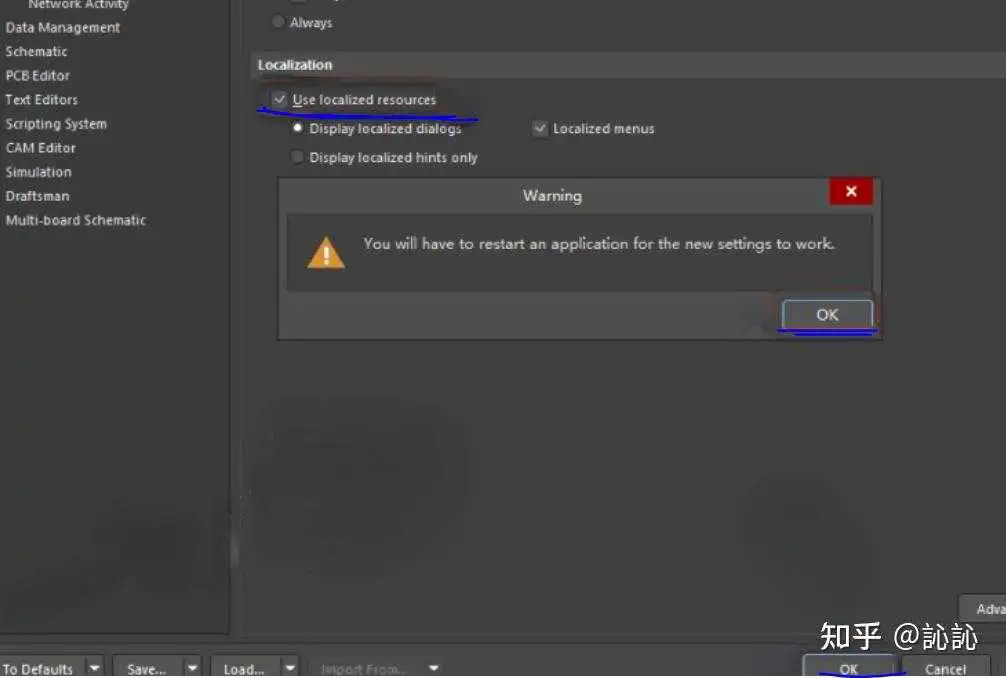

- 勾选 use localized resources,点击 OK,点击 OK(画线)

- 重新打开软件,安装完成

百度网盘

链接:https://pan.baidu.com/s/1x1pdYBd_xxTqCWAEnA1a_A

提取码:l51x

如果需要邮箱发送记得留言,小编看到后尽快安排

喜欢记得关注,记得收藏,记得分享,记得学习,留下疑惑,让我们共同进步……

到此这篇ad21安装及激活成功教程教程(ad20怎么激活成功教程安装教程)的文章就介绍到这了,更多相关内容请继续浏览下面的相关推荐文章,希望大家都能在编程的领域有一番成就!版权声明:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若内容造成侵权、违法违规、事实不符,请将相关资料发送至xkadmin@xkablog.com进行投诉反馈,一经查实,立即处理!

转载请注明出处,原文链接:https://www.xkablog.com/do-yfwjc/16926.html