Memory Hierarchy - 存储器层次结构

计算机系统将存储器分成若干层级 (memory hierarchy) ,越靠近 CPU 的存储器容量越小但访问速度越快。

1. Memory hierarchy (存储器层次结构)

Intel 北桥包含 2 个 channel,两组独立的线连接到各自的模块,每个 channel 包含 2 个DIMM。

Shared resources in multicore processors

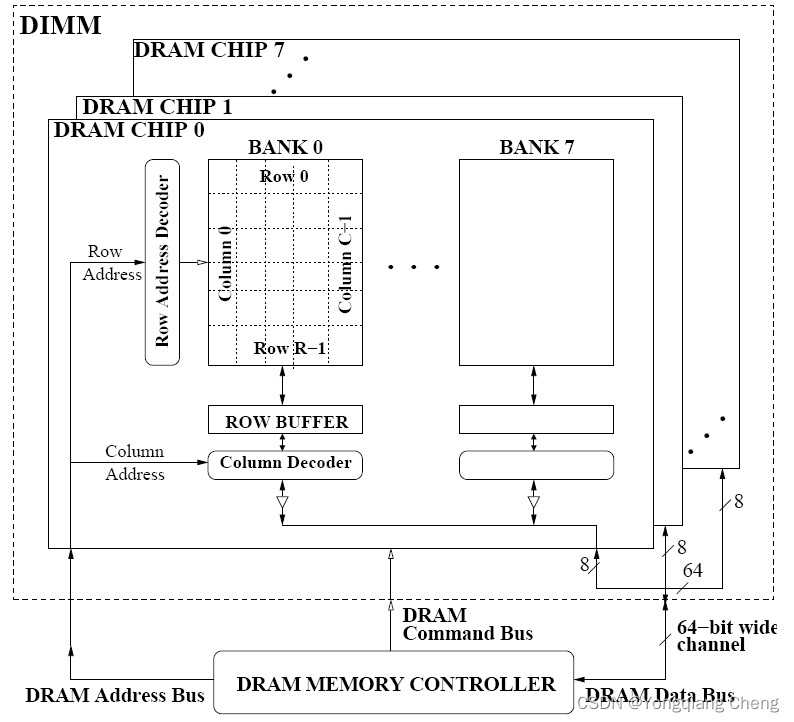

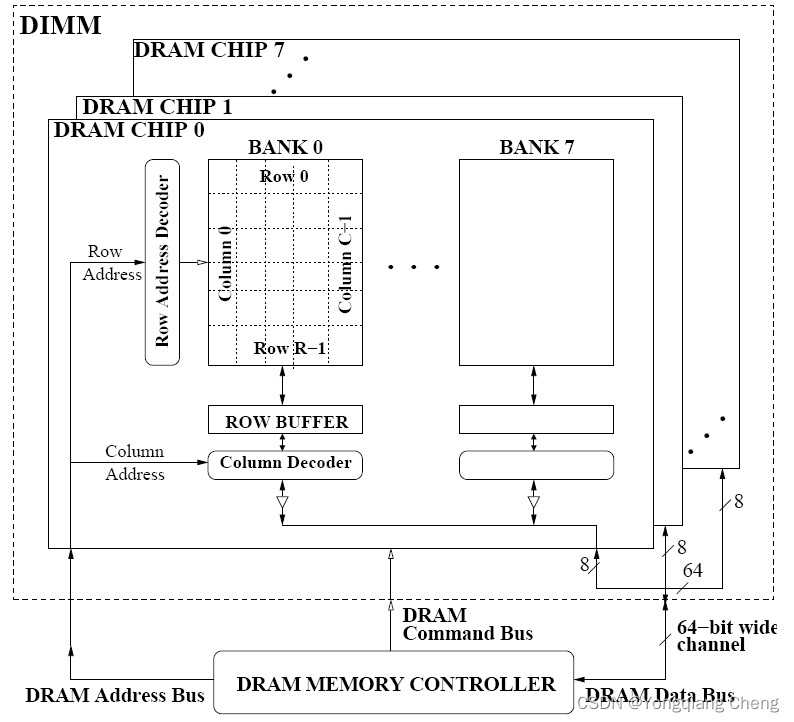

DRAM system organization

Module architecture

Generalized memory structure

2. Channel (通道)

相同的 rank 与 Chip Select (CS#) 连接在一起,当发出 CS# 信号时,相同 rank 内所有的 IC 颗粒会同时被 enable。2 个 rank 表示能接受两条 CS# 的信号,它们的名称为 S0# 与 S1#。1 个 rank 称为 1R,2 个 rank 称为 2R。相同 rank chip 的 CS# 全部与 DIMM 的 S0# 与 S1# 分别接在一起。

2.1 Dual channel (interleaved) mode

Dual channel (interleaved) mode configuration with two DIMMs

Dual channel (interleaved) mode configuration with three DIMMs

Dual channel (interleaved) mode configuration with four DIMMs

2.2 Single channel (asymmetric) mode

Single channel (asymmetric) mode configuration with one DIMM

Single channel (asymmetric) mode configuration with three DIMMs

2.3 Dual channel (flex mode)

Dual channel (flex mode) configuration with two DIMMs

2.4 DIMM per channel

2.5 T-topology

2.6 Daisy chain (菊花链)

daisy ['deɪzɪ]:n. 黛西,雏菊,延命菊,卓越的人或物 adj. 雏菊一样的,可爱的 Strict mapping of threads to ranks

Relaxed mapping of threads to ranks

3. Memory controller (内存控制器)

Memory controller

memory controller,MC:内存控制器 northbridge:北桥,北桥芯片 Cache blocks map to separate memory controllers

DRAM structure

Memory parallelism from independent banks and channels

Channels

4. DDR SDRAM

Comparison of DDR modules for desktop PCs (DIMM)

Comparison of memory modules for portable/mobile PCs (SO-DIMM)

random-access memory,RAM static random-access memory,static RAM or SRAM dynamic random-access memory,dynamic RAM or DRAM synchronous dynamic random-access memory,synchronous dynamic RAM or SDRAM double data rate synchronous dynamic random-access memory,DDR SDRAM double data rate,DDR single data rate,SDR dual in-line memory module,DIMM:双列直插内存模块 retroactively:adv. 逆动地 supersede [ˌsuːpə(r)ˈsiːd]:v. 取代 5. Rank

The term rank was created and defined by JEDEC, the memory industry standards group. On a DDR, DDR2, or DDR3 memory module, each rank has a 64-bits-wide data bus (72 bits wide on DIMMs that support ECC). The number of physical DRAMs depends on their individual widths. For example, a rank of ×8 (8-bits wide) DRAMs would consist of eight physical chips (nine if ECC is supported), but a rank of ×4 (4-bits wide) DRAMs would consist of 16 physical chips (18, if ECC is supported). Multiple ranks can coexist on a single DIMM, and modern DIMMs can consist of one rank (single rank), two ranks (dual rank), four ranks (quad rank), or eight ranks (octal rank).

rank 由内存行业标准组织 JEDEC 创建和定义。在 DDR, DDR2 or DDR3 内存模块上,每个 rank 都有一个 64 bits 宽的数据总线 (在支持 ECC 的 DIMM 上为 72 bits 宽)。物理 DRAM 的数量取决于它们各自的宽度。例如,一个 ×8 (8-bits wide) DRAM 将包含 8 个物理芯片 (如果支持 ECC,则为 9 个),但 ×4 (4-bits wide) DRAM 将包含 16 个物理芯片 (如果支持 ECC,则为 18 个)。多个 ranks 可以在单个 DIMM 上共存,现代 DIMM 可以由 1 rank (single rank), 2 ranks (dual rank), 4 ranks (quad rank), or 8 ranks (octal rank)。

single rank memory, dual rank memory and quad rank memory

single-sided module and double-sided module

single-sided single-rank, double-sided single-rank, double-sided dual-rank and double-sided quad-rank

x4 和 x8 代表每个 DRAM 芯片位宽。

双列直插内存模块 (dual in-line memory module,DIMM) 是指内存条印刷电路板正反面均有金手指与主板上的内存条槽接触,内存条称为 DIMM 条,主板上的内存槽称为 DIMM 槽。

single rank memory and dual rank memory

1 rank = 64 bit width (or 72 bit with ECC) single rank = 64 bit double rank = 64 bit + 64 bit quad rank = 64 bit + 64 bit + 64 bit + 64 bit - All chips comprising a rank are controlled at the same time (包含在一个 rank 的所有 chips 被同时控制)

- A DRAM module consists of one or more ranks

- If we have chips with 8-bit interface, to read 8 bytes in a single access, use 8 chips in a DIMM

quadrant [ˈkwɒdrənt]:n. 象限,象限仪,四分之一圆 octal ['ɒktl]:adj. 八的,八面的,八管脚的 layman ['leɪmən]:n. 外行,门外汉,非专业人员,在俗教徒 (非神职人员) single-sided:单面 double-sided:双面 A 64 bit wide DIMM (one rank)

2 Independent channels - 2 Memory controllers

6. Bank - Column - Row

DRAM bank

canonical [kəˈnɒnɪk(ə)l]:adj. 被收入真经篇目的,经典的,按照基督教教会法规的 n. (布道时应穿的) 法衣 transaction [træn'zækʃ(ə)n]:n. 处理,业务,办理 precharge:n. 预充电,预压力 DRAM operation

- A DRAM bank is a 2D array of cells:

rows x columns,each address is a<row, column>pair. - A DRAM row is also called a DRAM page

- sense amplifiers 也称为 row buffer

DRAM bank operation

128M x 8 bit DRAM chip

- Divide memory into

M (= n + 1)banks and interleave addresses across them

in bank (mod M)

at word (div M) - Interleaved memory increases memory bandwidth without wider bus (交错内存增加内存带宽而无需更宽的总线)

- Use parallelism in memory banks to hide memory latency (使用 memory banks 中的并行性来隐藏内存延迟)

interleave [ˌɪntə(r)ˈliːv]:v. 夹进,交错,交织

7. Transferring a cache block (传输缓存块)

References

Advanced Computer Architecture I

https://pages.cs.wisc.edu/~sinclair/courses/cs752/fall2020/handouts/lecture/12-dram.pdf

Software-Defined Physical Memory

https://www.betriebssysteme.org/wp-content/uploads/2017/04/Hillenbrand.pdf

Improving System Energy Efficiency with Memory Rank Subsetting

http://csl.stanford.edu/~christos/publications/2012.mcdimm.taco.pdf

DRAM Memory Module Rank Calculation

https://www.digikey.com/en/pdf/v/viking-technology/dram-memory-module-rank-calculation

Memory rank

https://en.wikipedia.org/wiki/Memory_rank

Memory geometry

https://en.wikipedia.org/wiki/Memory_geometry

Single Rank Memory VS Dual Rank Memory VS Quad Rank Memory

https://www.oempcworld.com/support/singlevsdualram.html

RAM (Random Access Memory), SIMMs, DIMM’s, RIMM’s

https://sites.google.com/site/shaunaatvcc2/memory/ram-random-access-memory-simms-dimm-s-rimm-s

Mengenal Istilah Memory Rank Pada Memori (RAM)

https://catatanteknisi.com/mengenal-istilah-memory-rank-pada-memori-ram/

Enabling big memory with emerging technologies

https://www.cs.utah.edu/~rajeev/pubs/shevgoor-phd.pdf

https://slideplayer.com/slide//

Single Rank VS Dual Rank

https://www.pcgaming.tech/single-rank-vs-dual-rank.html

Dual channel mode for DDR, DDR2, DDR3 and DDR4

https://www.compuram.de/blog/en/single-dual-and-multi-channel-memory-modes/

Wiring method of motherboard memory

https://www.programmersought.com/article//

DDR4

https://itgall.com/hardware/

DDR4 SDRAM - Understanding the Basics

https://www.systemverilog.io/ddr4-basics

2Rx8 and 1Rx8 DDR 的 Rank 与单面双面无关

https://www.strongpilab.com/ddr-2rx8-rank-not-side/

版权声明:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若内容造成侵权、违法违规、事实不符,请将相关资料发送至xkadmin@xkablog.com进行投诉反馈,一经查实,立即处理!

转载请注明出处,原文链接:https://www.xkablog.com/rfx/10500.html